8

EPSON

E0C6006 TECHNICAL MANUAL

CHAPTER 3: CPU, ROM, RAM

CHAPTER

3 CPU, ROM, RAM

3.1 CPU

The E0C6006 employs the E0C6200B core CPU, so that register configuration, instructions, and so forth

are virtually identical to those in other processors in the family using the E0C6200/6200A/6200B. Refer to

the "E0C6200/6200A Core CPU Manual" for details of the E0C6200B.

Note the following points with regard to the E0C6006:

(1) The E0C6006 does not support the SLEEP function, therefore the SLP instruction cannot be used.

(2) Because the ROM capacity is 2,048 words, 12 bits per word, bank bits are unnecessary, and PCB and

NBP are not used.

(3) The RAM page is set to 0 only, so the page part (XP, YP) of the index register that specifies addresses is

invalid.

PUSH XP POP XP LD XP,r LD r,XP

PUSH YP POP YP LD YP,r LD r,YP

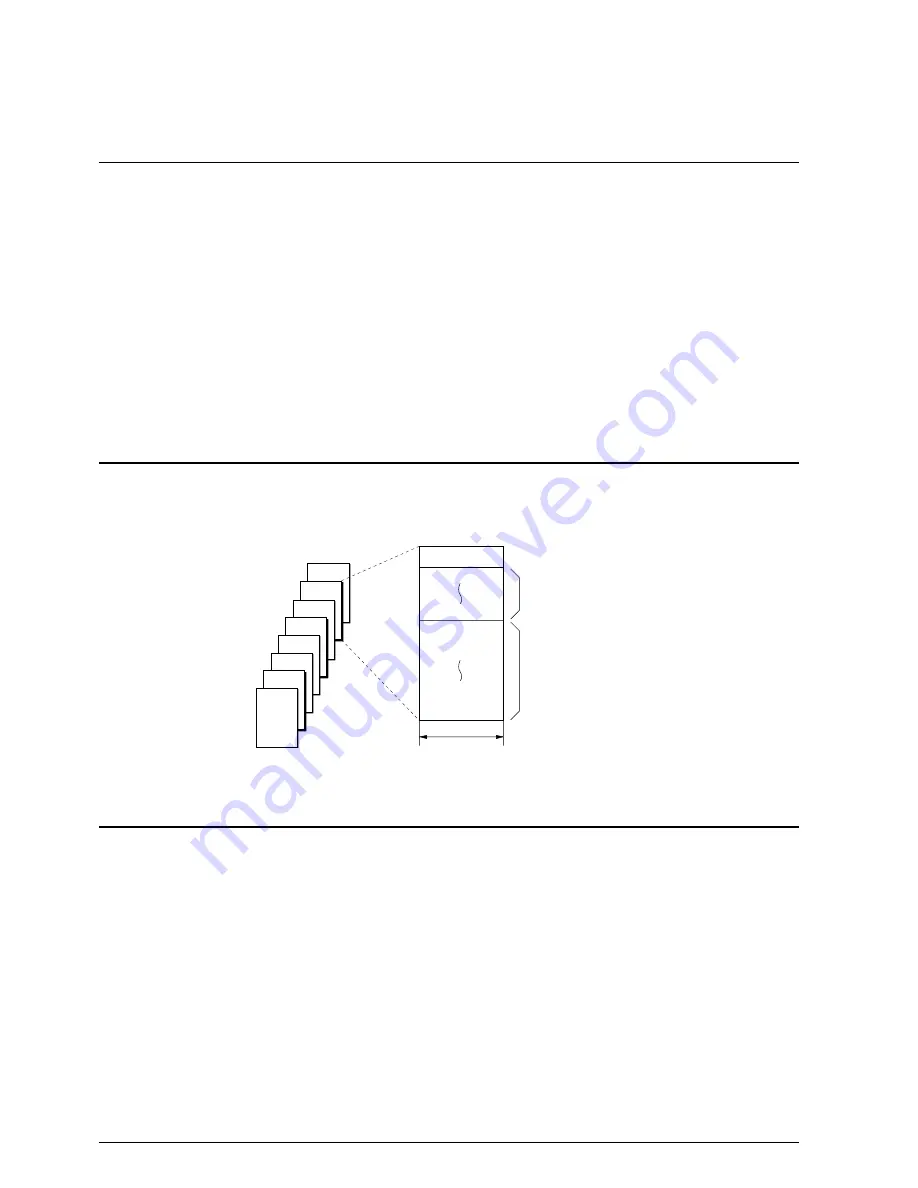

3.2 ROM

The built-in ROM, a mask ROM for the program, has a capacity of 2,048

×

12-bit steps. The program area

is 8 pages (0–7), each consisting of 256 steps (00H–FFH). After an initial reset, the program start address is

set to page 1, step 00H. The interrupt vectors are allocated to page 1, steps 01H–07H.

Step 00H

Step 07H

Step 08H

Step FFH

12 bits

Program start address

Interrupt vector area

Bank 0

Program area

Page 0

Page 1

Page 2

Page 3

Page 4

Page 5

Step 01H

Page 6

Page 7

Fig. 3.2.1 ROM configuration

3.3 RAM

The RAM, a data memory for storing a variety of data, has a capacity of 128 words, 4-bit words. When

programming, keep the following points in mind:

(1) Part of the data memory is used as stack area when saving subroutine return addresses and registers,

so be careful not to overlap the data area and stack area.

(2) Subroutine calls and interrupts take up three words on the stack.

(3) Data memory 000H–00FH is the memory area pointed by the register pointer (RP).