Coprocessor Interface

7-10

Copyright © 2000 ARM Limited. All rights reserved.

ARM DDI 0186A

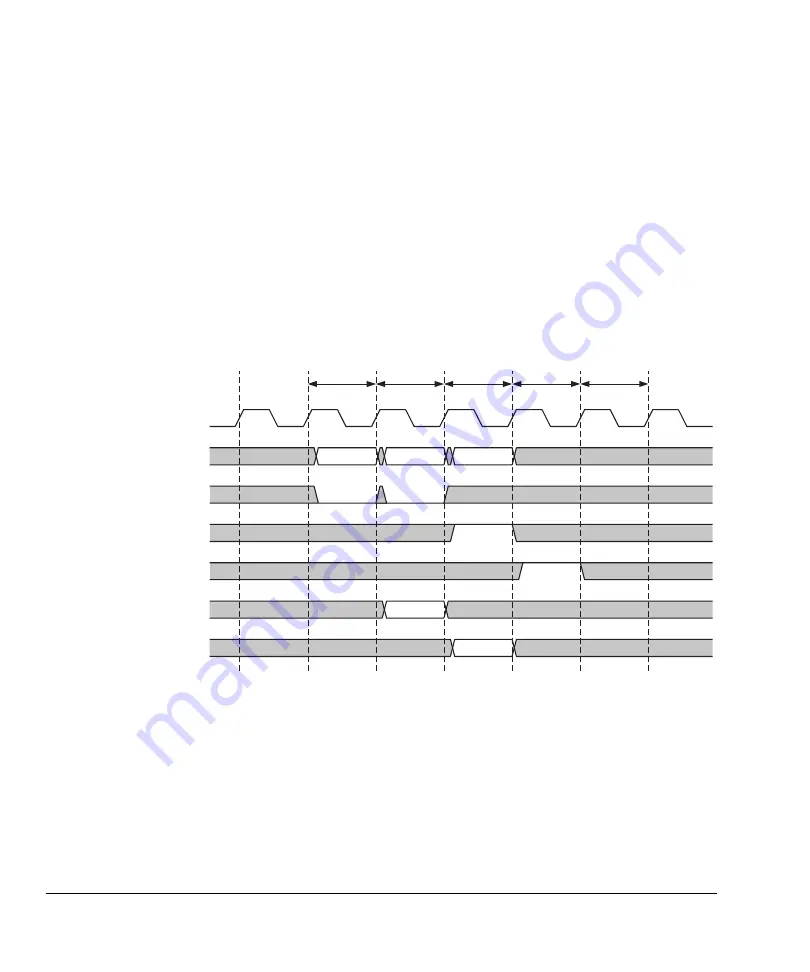

7.5

CDP

CDP

instructions normally execute in a single cycle. Like all the previous cycles,

nCPMREQ

is driven LOW to signal when an instruction is entering the Decode and

then the Execute stage of the pipeline:

•

if the instruction really is to be executed, the

CPPASS

signal is driven HIGH

during the Execute cycle

•

if the coprocessor can execute the instruction immediately it drives

CHSDE[1:0]

with LAST

•

if the instruction requires a busy-wait cycle, the coprocessor drives

CHSDE[1:0]

with WAIT and then

CHSEX[1:0]

with LAST.

Figure 7-4 shows a cancelled

CDP

due to the previous instruction causing a Data Abort.

Figure 7-4 Late cancelled CDP

The

CDP

instruction enters the Execute stage of the pipeline and is signaled to execute

by

CPASS

. In the following cycle

CPLATECANCEL

is asserted. This causes the

coprocessor to terminate execution of the

CDP

instruction and for it to cause no state

changes to the coprocessor.

CLK

CPINSTR[31:0]

CPPASS

CHSEX[1:0]

CPLATECANCEL

CHSDE[1:0]

nCPMREQ

Fetch

Decode

Execute

Memory

(late cancelled)

Instruction

aborted

CPRT

LAST

Ignored

Coprocessor

pipeline

Содержание ARM966E-S

Страница 6: ...Contents vi Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Страница 20: ...Introduction 1 4 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Страница 48: ...Tightly coupled SRAM 4 12 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Страница 80: ...Bus Interface Unit 6 20 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Страница 118: ...Debug Support 8 26 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Страница 130: ...Test Support 10 8 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Страница 142: ...Instruction cycle timings 11 12 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Страница 158: ...Signal Descriptions A 16 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Страница 176: ...AC Parameters B 18 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...