Direct Memory Access (DMA)

ARM DDI 0186A

Copyright © 2000 ARM Limited. All rights reserved.

5-11

5.3

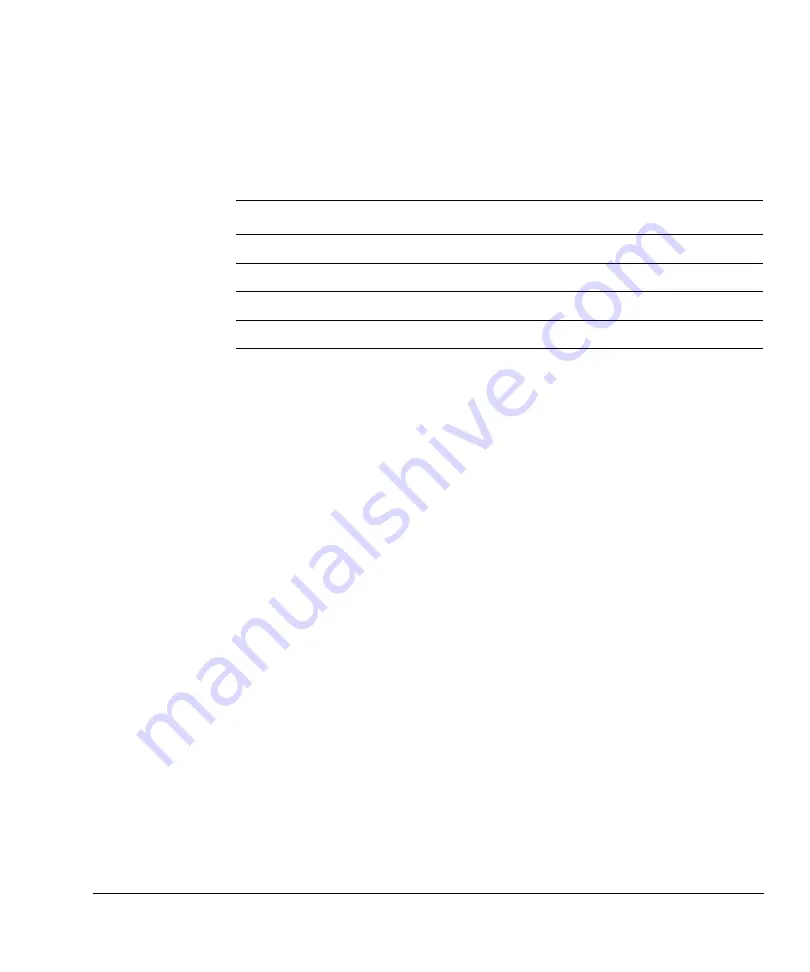

DMAENABLE setup and hold cycles

Table 5-2 shows the minimum number of setup cycles and hold cycles for

DMAENABLE

with respect to

DMAnREQ

for both single and dual-port RAMs.

To reduce power consumption,

DMAENABLE

must be taken LOW when DMA

accesses are not taking place or if DMA is not implemented.

Table 5-2 DMAENABLE setup and hold cycles with respect to DMAnREQ

Operation

Setup

Hold

Dual-port RAM DMA read

1

1

Dual-port RAM DMA write

1

0

Single-port RAM DMA read

1

1

Single-port RAM DMA write

1

0

Содержание ARM966E-S

Страница 6: ...Contents vi Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Страница 20: ...Introduction 1 4 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Страница 48: ...Tightly coupled SRAM 4 12 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Страница 80: ...Bus Interface Unit 6 20 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Страница 118: ...Debug Support 8 26 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Страница 130: ...Test Support 10 8 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Страница 142: ...Instruction cycle timings 11 12 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Страница 158: ...Signal Descriptions A 16 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Страница 176: ...AC Parameters B 18 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...