Bus Interface Unit

6-4

Copyright © 2000 ARM Limited. All rights reserved.

ARM DDI 0186A

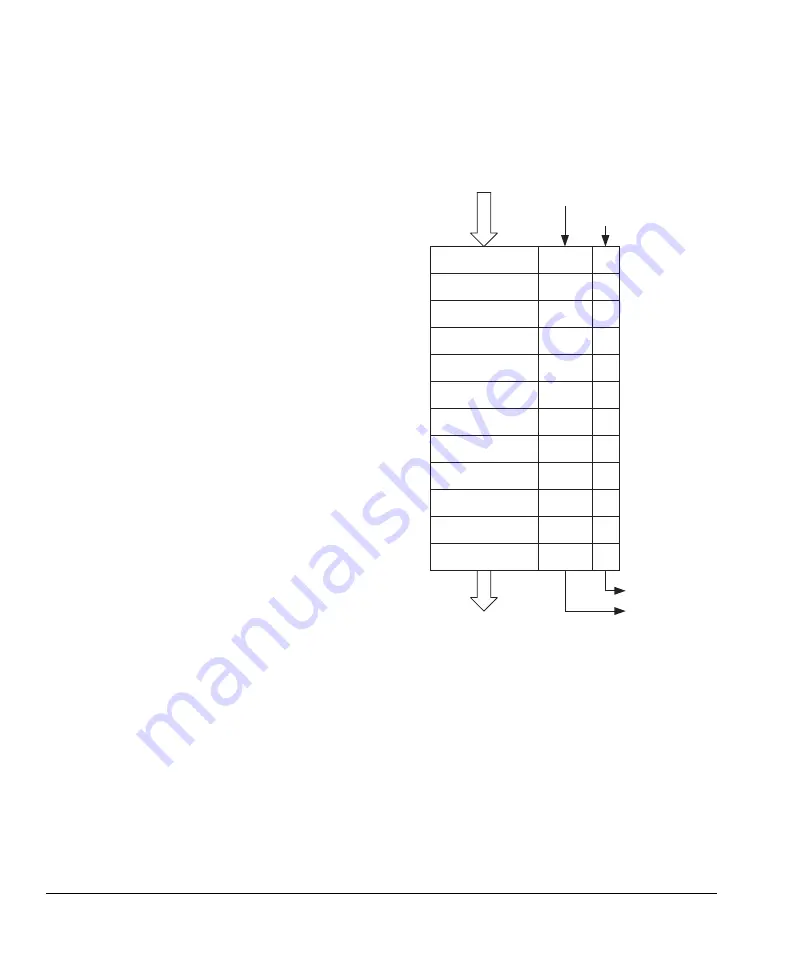

STMIA r13!,{r2-r4} ; store three registers to the stack

STRB

r5,[r6]

; store byte

STMIA r13!,{r3-r4} ; store two registers to the stack

STR

r7,[r2]

; single store

Figure 6-1 Write buffer FIFO content example

6.2.2

Draining write data from the write buffer

The write buffer can drain

naturally

where AHB writes occur whenever data is

committed to the FIFO. The core is only stalled, if the write buffer overflows. However,

there are times when a complete drain of the write buffer is

enforced

.

Data

Address

Data

Data

Address

Data

Address

Data

Data

Data

Address

r7

r2

r4

r3

r13

r5

r6

r4

r3

r2

r13

A

Word

A

Word

A

Byte

A

Word

S

S

S

From ARM9E-S CLK domain

Address and size marker

Sequentiality marker

To AHB HCLK domain

To BIU control

Содержание ARM966E-S

Страница 6: ...Contents vi Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Страница 20: ...Introduction 1 4 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Страница 48: ...Tightly coupled SRAM 4 12 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Страница 80: ...Bus Interface Unit 6 20 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Страница 118: ...Debug Support 8 26 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Страница 130: ...Test Support 10 8 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Страница 142: ...Instruction cycle timings 11 12 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Страница 158: ...Signal Descriptions A 16 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Страница 176: ...AC Parameters B 18 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...