SRAM Stall Cycles

ARM DDI 0186A

Copyright © 2000 ARM Limited. All rights reserved.

C-5

Figure C-4 Data read from I-SRAM

The stall cycle is only incurred for the first read of a read instruction. If an

LDM

is

performed, there is a stall cycle inserted only for the first read of the

LDM

. Back-to- back

LDR

s will incur a stall cycle at the start of each

LDR

.

Data read followed by instruction fetch

Data reads to the I-SRAM are pipelined. An instruction fetch in the cycle after a data

read request coincides with the stalled data read and so the instruction fetch is stalled

for 1 cycle. This is shown in on page C-6.

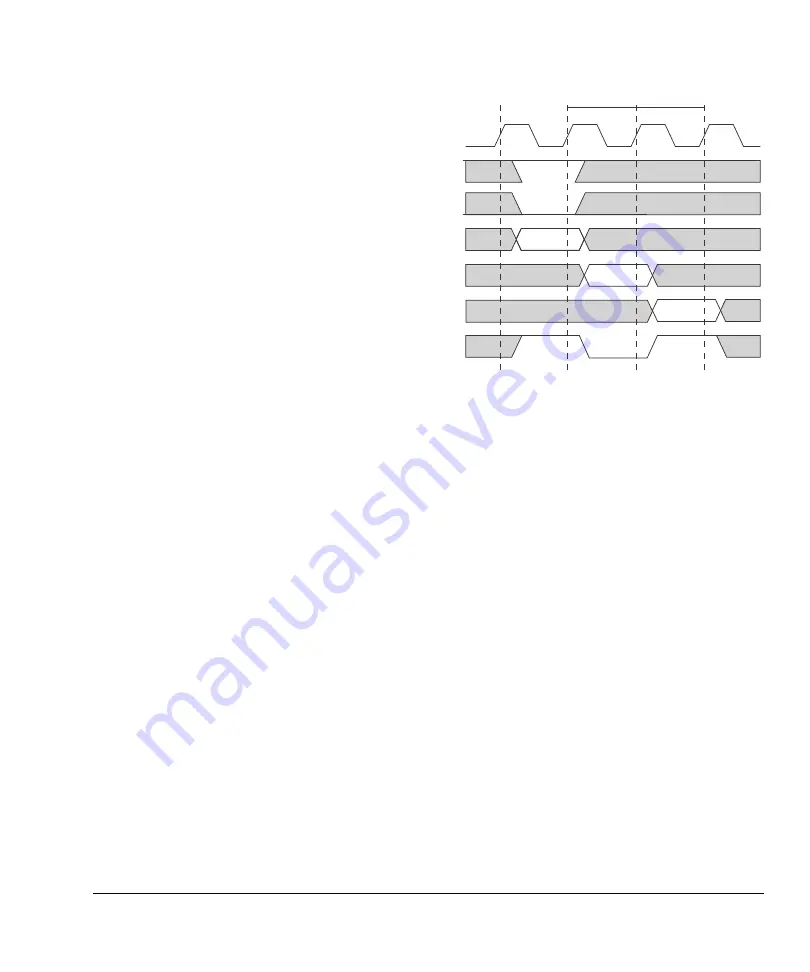

CLK

DnMREQ

DnRW

DA[31:0]

SRAM Addr

RDATA[31:0]

SYSCLKEN

SRAM

stall cycle

Addr A (read)

Addr A

Read data

SRAM

read cycle

Содержание ARM966E-S

Страница 6: ...Contents vi Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Страница 20: ...Introduction 1 4 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Страница 48: ...Tightly coupled SRAM 4 12 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Страница 80: ...Bus Interface Unit 6 20 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Страница 118: ...Debug Support 8 26 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Страница 130: ...Test Support 10 8 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Страница 142: ...Instruction cycle timings 11 12 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Страница 158: ...Signal Descriptions A 16 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Страница 176: ...AC Parameters B 18 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...