ADSP-2126x SHARC Processor Hardware Reference

A-5

Registers Reference

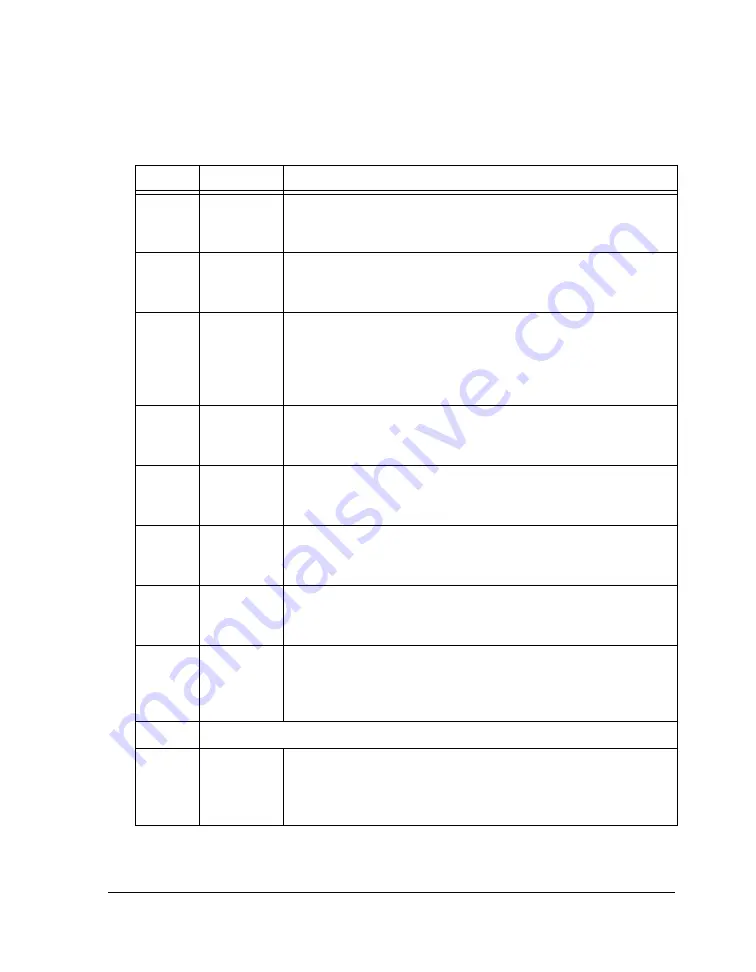

Table A-2. Mode Control 1 Register (MODE1) Bit Descriptions

Bit

Name

Description

0

BR8

Bit-Reverse Addressing For Index I8 Enable.

Enables (bit reversed if

set, = 1) or disables (normal if cleared, = 0) bit-reversed addressing for

accesses that are indexed with DAG2 register I8.

1

BR0

Bit-Reverse Addressing For Index I0 Enable.

Enables (bit reversed if

set, = 1) or disables (normal if cleared, = 0) bit-reversed addressing for

accesses that are indexed with DAG1 register I0.

2

SRCU

MRx Result Registers Swap Enable.

Enables the swapping of the

MRF and MRB registers contents if set (= 1). This can be used as

foreground and background registers. In SIMD Mode the swapping

also performed between MSF and MSB registers.

This works similar to the RF swapping instructions Rx<->Sx.

3

SRD1H

Secondary Registers For DAG1 High Enable.

Enables (use secondary

if set, = 1) or disables (use primary if cleared, = 0) secondary DAG1

registers for the upper half (I, M, L, B7–4) of the address generator.

4

SRD1L

Secondary Registers For DAG1 Low Enable.

Enables (use secondary

if set, = 1) or disables (use primary if cleared, = 0) secondary DAG1

registers for the lower half (I, M, L, B3–0) of the address generator.

5

SRD2H

Secondary Registers For DAG2 High Enable.

Enables (use secondary

if set, = 1) or disables (use primary if cleared, = 0) secondary DAG2

registers for the upper half (I, M, L, B15–12) of the address generator.

6

SRD2L

Secondary Registers For DAG2 Low Enable.

Enables (use secondary

if set, = 1) or disables (use primary if cleared, = 0) secondary DAG2

registers for the lower half (I, M, L, B11–8) of the address generator.

7

SRRFH

Secondary Registers For Register File High Enable.

Enables (use sec-

ondary if set, = 1) or disables (use primary if cleared, = 0) secondary

data registers for the upper half (R15-R8/S15-S8) of the computa-

tional units.

9–8

Reserved

10

SRRFL

Secondary Registers For Register File Low Enable.

Enables (use sec-

ondary if set, = 1) or disables (use primary if cleared, = 0) secondary

data registers for the lower half (R7-R0/S7-S0) of the computational

units.

Содержание ADSP-21261 SHARC

Страница 30: ...Contents xxx ADSP 2126x SHARC Processor Hardware Reference ...

Страница 40: ...Register Diagram Conventions xl ADSP 2126x SHARC Processor Hardware Reference ...

Страница 58: ...Differences From Previous SHARCs 1 18 ADSP 2126x SHARC Processor Hardware Reference ...

Страница 112: ...Secondary Processing Element PEy 2 54 ADSP 2126x SHARC Processor Hardware Reference ...

Страница 178: ...Summary 3 66 ADSP 2126x SHARC Processor Hardware Reference ...

Страница 204: ...DAG Instruction Summary 4 26 ADSP 2126x SHARC Processor Hardware Reference ...

Страница 322: ...Setting Up DMA 7 32 ADSP 2126x SHARC Processor Hardware Reference ...

Страница 436: ...SPORT Programming Examples 9 86 ADSP 2126x SHARC Processor Hardware Reference ...

Страница 521: ...ADSP 2126x SHARC Processor Hardware Reference 11 31 Input Data Port rts IDP_ISR end ...

Страница 522: ...Input Data Port Programming Example 11 32 ADSP 2126x SHARC Processor Hardware Reference ...

Страница 590: ...Timer Programming Examples 14 20 ADSP 2126x SHARC Processor Hardware Reference ...

Страница 796: ...I O Processor Registers A 174 ADSP 2126x SHARC Processor Hardware Reference ...

Страница 800: ...B 4 ADSP 2126x SHARC Processor Core Manual ...

Страница 846: ...Index I 36 ADSP 2126x SHARC Processor Hardware Reference ...