Verdin Carrier Board Design Guide

Preliminary

– Subject to Change

Toradex AG l Ebenaustrasse 10 l 6048 Horw l Switzerland l +41 41 500 48 00 l

l

Page | 27

Verdin

Pin

Verdin

Signal Name

I/O

Type

Power

Rail

Description

187

USB_2_OC#

I

OD

1.8V

Over current input signal

Table 10: USB_2 Signals

SuperSpeed signals are basically PCIe signals and therefore support polarity inversion. This means

the positive and negative signal pins can be inverted in order to simplify the layout by avoiding

crossover of the signals. It is not permitted to swap the receiving signals with the transmitting ones.

Important, the USB 2.0 data signals do not support polarity inversion; USB_x_D_P and USB_x_D_N

cannot be swapped.

2.4.2

Reference Schematics

As the additional SuperSpeed USB 3.x data signals are PCIe signals at the physical layer.

Therefore, the schematic requirements are like those for PCIe. This means AC coupling capacitors

are required. The placement of the capacitors depends on whether the USB 3.x device is populated

on the carrier board (device-down) or is connected over a cable. The USB 2.0 data signals do not

need any coupling capacitors.

The SuperSpeed interface consists of a pair of transmitting (TX) and receiving (RX) traces.

Unfortunately, the names RX and TX can be confusing as the host transmitter needs to be

connected to the receiver of the device and vice versa. Normally, the signals are named after the

host until they reach the pins of the USB device. Therefore, the transmitting pins on the Verdin

module should be called TX on the carrier board while the receiving pins should be called RX.

Please read carefully the datasheet of the USB device (device-down) in order to ensure RX and TX

are not confused.

2.4.2.1

USB 2.0 OTG Schematic Example

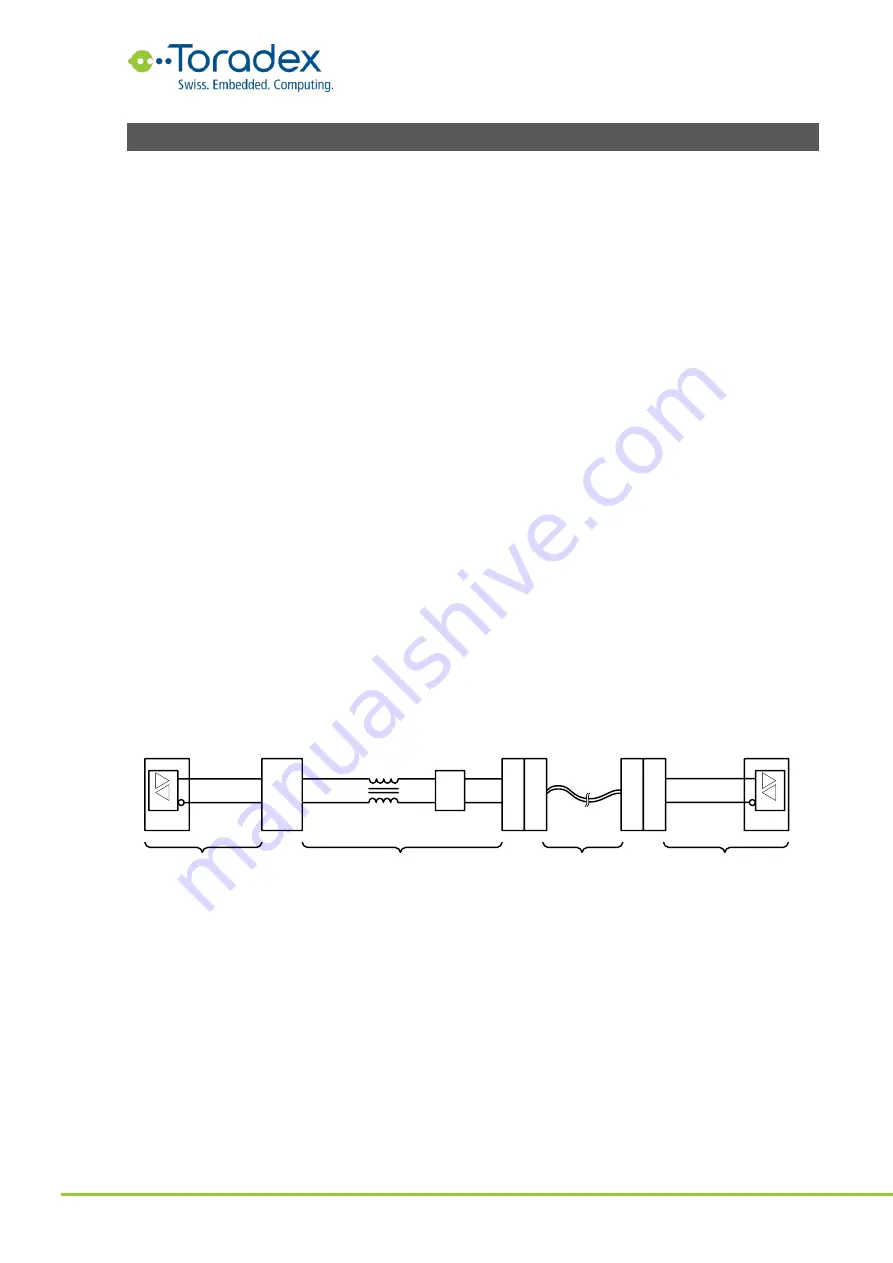

If the USB signals are externally available, ESD protection diodes need to be placed on all of the

USB signals. Make sure that the protection diodes are USB 2.0 compliant. The USB signals

additionally require a common mode choke for passing EMI testing. Use common mode chokes

that are specified for High-speed USB 2.0.

Figure 16: USB 2.0 OTG Block Diagram

The USB_1_ID signal is used to detect which type of USB connector is plugged into the OTG jack

(Micro-AB jack). When a Micro-A connector is inserted, the ID pin is connected to signal ground,

causing the OTG port to be configured as a host. If a Micro-B USB connector is inserted, the ID pin

is left unbiased and the OTG port will be configured as a slave device. For the USB_1_ID signal a

pull-up resistor to 1.8V is needed.

The USB_1_VBUS input signal is only used if the OTG port is in client mode (Micro-B USB connector

plugged in). The signal is used to detect whether a host is connected on the other end of the USB

cable. This signal is 5V tolerant and can be connected directly to the power supply pin of the USB

jack. ESD protection diodes should be used for this signal.

The USB_1_EN signal is used to enable the USB bus power supply if a Micro-A USB connector is

plugged in. The USB_1_EN signal has a I/O level of 1.8V. Depending on the power switch IC, a

simple level shifter may be required.

Verdin Module

Carrier Board

USB_1_D_P

USB_1_D_N

USB_1_D_P

USB_1_D_N

RX/TX

U

SB

2

.0

O

TG

Con

trol

le

r

USB 2.0/1.1

M

o

du

le

C

o

nn

ect

o

r

US

B

M

icro

-AB

O

TG

R

ece

ptac

le

D+

D-

US

B

2

.0

H

o

st

USB 2.0/1.1

RX/TX

USB Host

USB Cable

TVS

Diode

US

B

M

icro

-B

O

TG

P

lug

US

B

A

P

lu

g

U

SB

A

R

ece

pta

cl

e