TMS320F2810, TMS320F2811, TMS320F2812

TMS320C2810, TMS320C2811, TMS320C2812

SPRS174T – APRIL 2001 – REVISED MAY 2012

www.ti.com

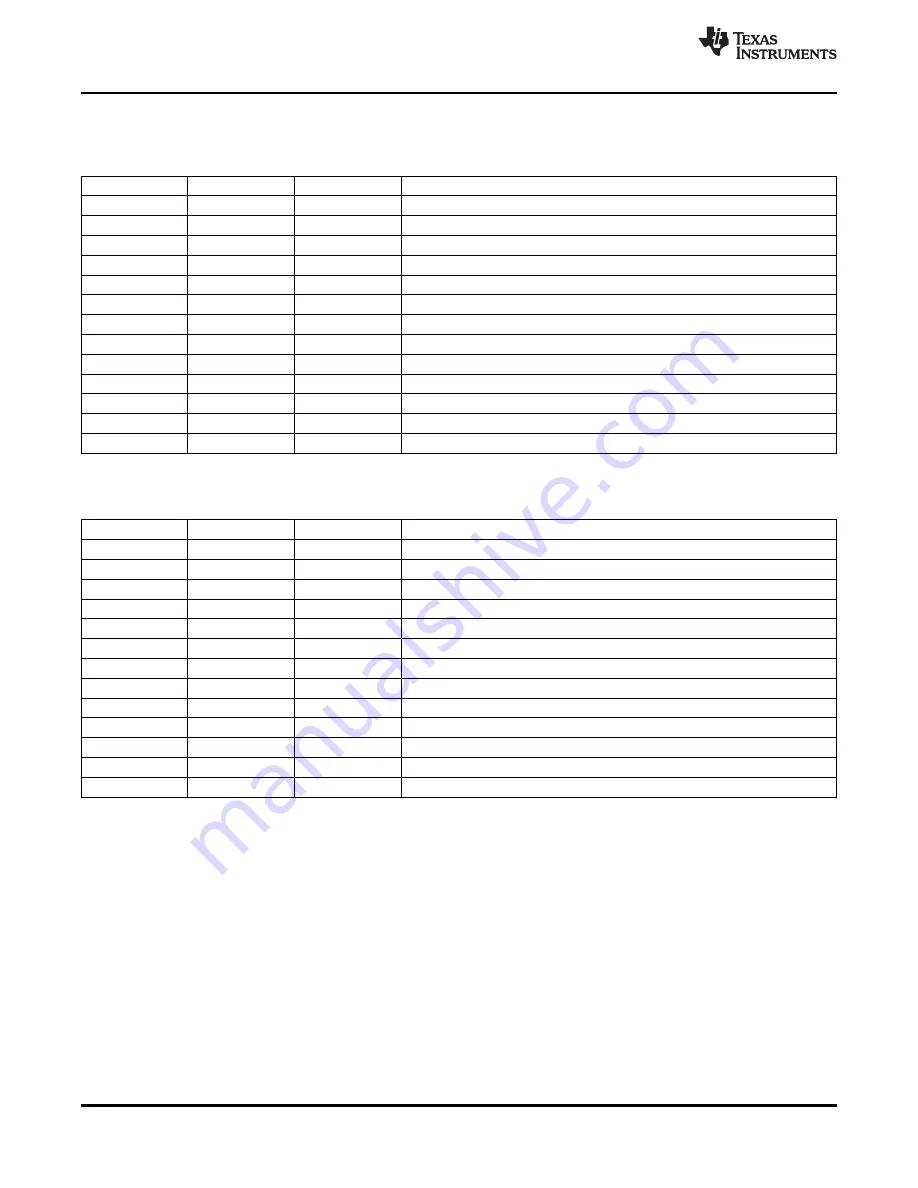

The SCI port operation is configured and controlled by the registers listed in

Table 4-8

and

Table 4-9

.

Table 4-8. SCI-A Registers

NAME

ADDRESS

SIZE (x16)

DESCRIPTION

SCICCRA

0x00 7050

1

SCI-A Communications Control Register

SCICTL1A

0x00 7051

1

SCI-A Control Register 1

SCIHBAUDA

0x00 7052

1

SCI-A Baud Register, High Bits

SCILBAUDA

0x00 7053

1

SCI-A Baud Register, Low Bits

SCICTL2A

0x00 7054

1

SCI-A Control Register 2

SCIRXSTA

0x00 7055

1

SCI-A Receive Status Register

SCIRXEMUA

0x00 7056

1

SCI-A Receive Emulation Data Buffer Register

SCIRXBUFA

0x00 7057

1

SCI-A Receive Data Buffer Register

SCITXBUFA

0x00 7059

1

SCI-A Transmit Data Buffer Register

SCIFFTXA

(1)

0x00 705A

1

SCI-A FIFO Transmit Register

SCIFFRXA

(1)

0x00 705B

1

SCI-A FIFO Receive Register

SCIFFCTA

(1)

0x00 705C

1

SCI-A FIFO Control Register

SCIPRIA

0x00 705F

1

SCI-A Priority Control Register

(1)

These registers are new registers for the FIFO mode.

Table 4-9. SCI-B Registers

(1)

NAME

ADDRESS

SIZE (x16)

DESCRIPTION

SCICCRB

0x00 7750

1

SCI-B Communications Control Register

SCICTL1B

0x00 7751

1

SCI-B Control Register 1

SCIHBAUDB

0x00 7752

1

SCI-B Baud Register, High Bits

SCILBAUDB

0x00 7753

1

SCI-B Baud Register, Low Bits

SCICTL2B

0x00 7754

1

SCI-B Control Register 2

SCIRXSTB

0x00 7755

1

SCI-B Receive Status Register

SCIRXEMUB

0x00 7756

1

SCI-B Receive Emulation Data Buffer Register

SCIRXBUFB

0x00 7757

1

SCI-B Receive Data Buffer Register

SCITXBUFB

0x00 7759

1

SCI-B Transmit Data Buffer Register

SCIFFTXB

(2)

0x00 775A

1

SCI-B FIFO Transmit Register

SCIFFRXB

(2)

0x00 775B

1

SCI-B FIFO Receive Register

SCIFFCTB

(2)

0x00 775C

1

SCI-B FIFO Control Register

SCIPRIB

0x00 775F

1

SCI-B Priority Control Register

(1)

Registers in this table are mapped to peripheral bus 16 space. This space only allows 16-bit accesses. 32-bit accesses produce

undefined results.

(2)

These registers are new registers for the FIFO mode.

78

Peripherals

Copyright © 2001–2012, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Link(s):

TMS320F2810 TMS320F2811 TMS320F2812 TMS320C2810 TMS320C2811 TMS320C2812