MSP430F5338, MSP430F5336, MSP430F5335, MSP430F5333

SLAS721D – AUGUST 2010 – REVISED DECEMBER 2015

www.ti.com

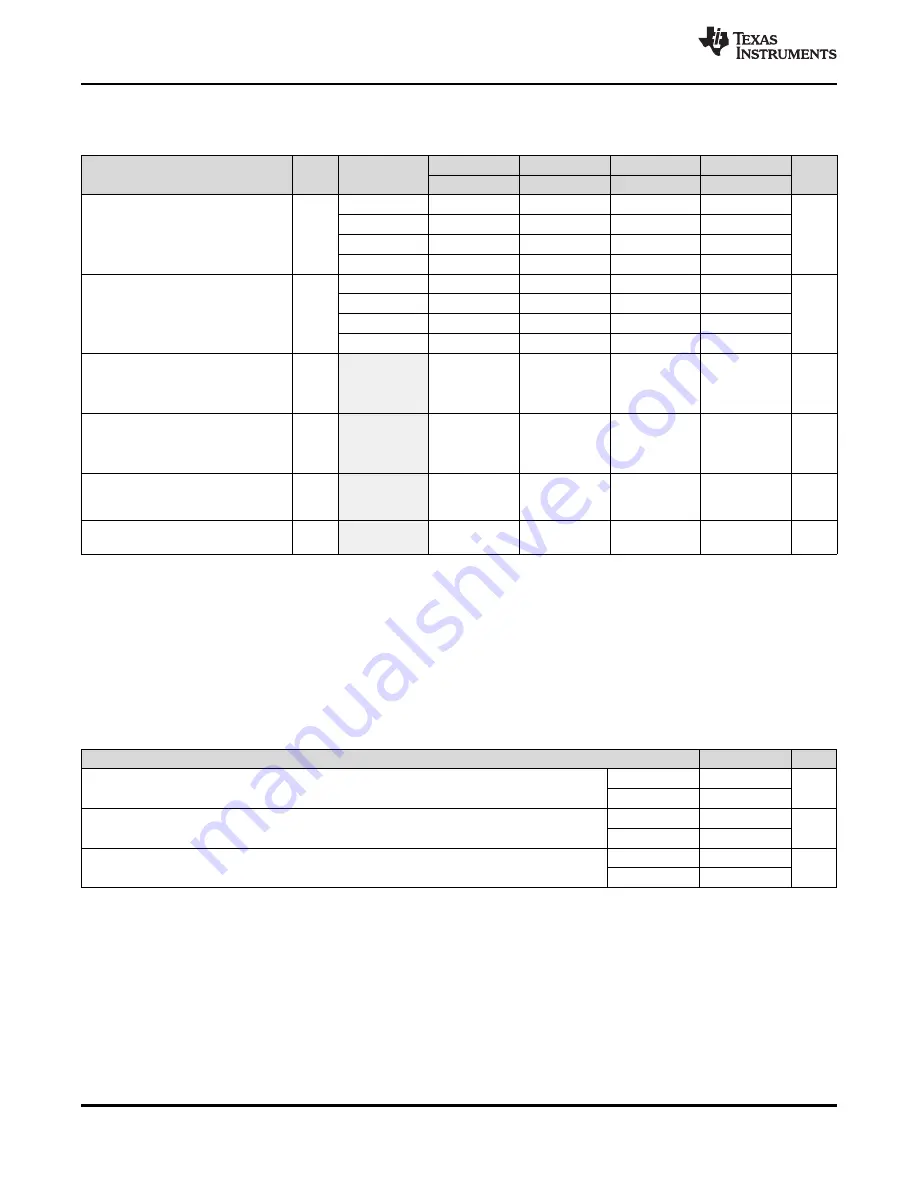

Low-Power Mode Supply Currents (Into V

CC

) Excluding External Current (continued)

over recommended ranges of supply voltage and operating free-air temperature (unless otherwise noted)

(1)(2)

–40°C

25°C

60°C

85°C

PARAMETER

V

CC

PMMCOREVx

UNIT

TYP

MAX

TYP

MAX

TYP

MAX

TYP

MAX

0

0.9

1.2

1.9

4.0

5.9

10.3

Low-power mode 3,

1

0.9

1.2

4.1

6.0

I

LPM3,

VLO mode, Watchdog

3 V

µA

VLO,WDT

2

1.0

1.3

4.2

6.1

enabled

(7) (4)

3

1.0

1.3

2.2

4.3

6.3

11.3

0

0.9

1.1

1.8

3.9

5.8

10

1

0.9

1.1

4.0

5.9

I

LPM4

Low-power mode 4

(8) (4)

3 V

µA

2

1.0

1.2

4.1

6.1

3

1.0

1.2

2.1

4.2

6.2

11

Low-power mode 3.5

I

LPM3.5,

(LPM3.5) current with

3 V

0.5

0.8

1.4

µA

RTC,VCC

active RTC into primary

supply pin DV

CC

(9)

Low-power mode 3.5

I

LPM3.5,

(LPM3.5) current with

3 V

0.6

0.8

1.4

µA

RTC,VBAT

active RTC into backup

supply pin VBAT

(10)

Total low-power mode

I

LPM3.5,

3.5 (LPM3.5) current

3 V

1.0

1.1

1.3

1.6

2.8

µA

RTC,TOT

with active RTC

(11)

Low-power mode 4.5

I

LPM4.5

3 V

0.2

0.3

0.6

0.7

0.9

1.4

µA

(LPM4.5)

(12)

(7)

Current for watchdog timer clocked by VLO included.

CPUOFF = 1, SCG0 = 1, SCG1 = 1, OSCOFF = 0 (LPM3), f

ACLK

= f

MCLK

= f

SMCLK

= f

DCO

= 0 MHz

LDO disabled (LDOEN = 0).

(8)

CPUOFF = 1, SCG0 = 1, SCG1 = 1, OSCOFF = 1 (LPM4), f

DCO

= f

ACLK

= f

MCLK

= f

SMCLK

= 0 MHz

LDO disabled (LDOEN = 0).

(9)

V

VBAT

= V

CC

- 0.2 V, f

DCO

= f

MCLK

= f

SMCLK

= 0 MHz, f

ACLK

= 32768 Hz, PMMREGOFF = 1, RTC in backup domain active

(10) V

VBAT

= V

CC

- 0.2 V, f

DCO

= f

MCLK

= f

SMCLK

= 0 MHz, f

ACLK

= 32768 Hz, PMMREGOFF = 1, RTC in backup domain active, no

current drawn on VBAK

(11) f

DCO

= f

MCLK

= f

SMCLK

= 0 MHz, f

ACLK

= 32768 Hz, PMMREGOFF = 1, RTC in backup domain active, no current drawn on VBAK

(12) Internal regulator disabled. No data retention.

CPUOFF = 1, SCG0 = 1, SCG1 = 1, OSCOFF = 1, PMMREGOFF = 1 (LPM4.5), f

DCO

= f

ACLK

= f

MCLK

= f

SMCLK

= 0 MHz

5.6

Thermal Resistance Characteristics

PARAMETER

VALUE

UNIT

QFP (PZ)

122

θ

JA

Junction-to-ambient thermal resistance, still air

(1)

°C/W

BGA (ZQW)

108

QFP (PZ)

83

θ

JC(TOP)

Junction-to-case (top) thermal resistance

(2)

°C/W

BGA (ZQW)

72

QFP (PZ)

98

θ

JB

Junction-to-board thermal resistance

(3)

°C/W

BGA (ZQW)

76

(1)

The junction-to-ambient thermal resistance under natural convection is obtained in a simulation on a JEDEC-standard, High-K board, as

specified in JESD51-7, in an environment described in JESD51-2a.

(2)

The junction-to-case (top) thermal resistance is obtained by simulating a cold plate test on the package top. No specific JEDEC-

standard test exists, but a close description can be found in the ANSI SEMI standard G30-88.

(3)

The junction-to-board thermal resistance is obtained by simulating in an environment with a ring cold plate fixture to control the PCB

temperature, as described in JESD51-8.

18

Specifications

Copyright © 2010–2015, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Links:

MSP430F5338 MSP430F5336 MSP430F5335 MSP430F5333

Summary of Contents for MSP430F5333

Page 110: ......