SWRS037B – JANUARY 2006 – REVISED MARCH 2015

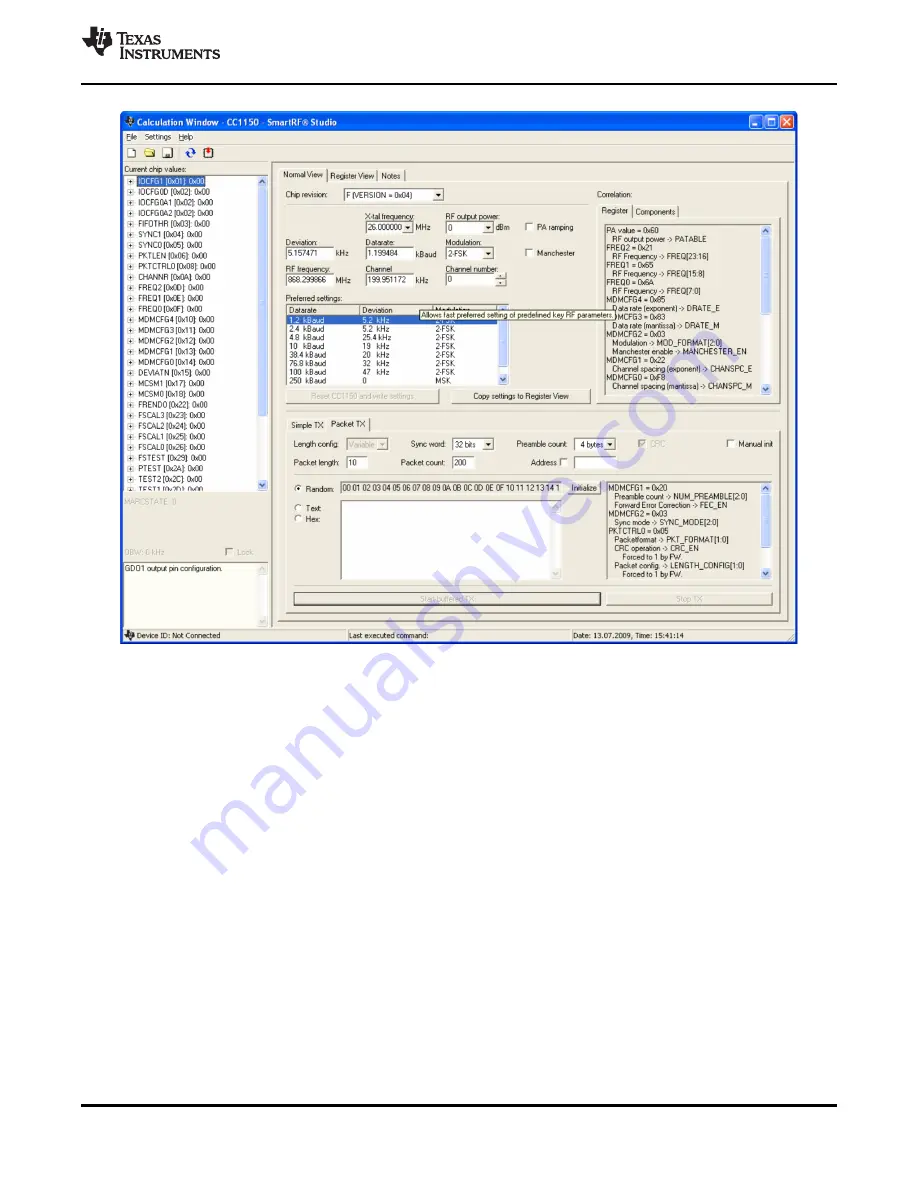

Figure 5-3. SmartRF Studio User Interface

5.5

4-wire Serial Configuration and Data Interface

CC1150 is configured via a simple 4-wire SPI-compatible interface (SI, SO, SCLK and CSn) where

CC1150 is the slave. This interface is also used to read and write buffered data. All address and data

transfer on the SPI interface is done most significant bit first.

All transactions on the SPI interface start with a header byte containing a read/write bit, a burst access bit

and a 6-bit address.

During address and data transfer, the CSn pin (Chip Select, active low) must be kept low. If CSn goes

high during the access, the transfer will be cancelled. The timing for the address and data transfer on the

SPI interface is shown in

with reference to

When CSn is pulled low, the MCU must wait until the CC1150 SO pin goes low before starting to transfer

the header byte. This indicates that the voltage regulator has stabilized and the crystal is running. Unless

the chip is in the SLEEP or XOFF states, the SO pin will always go low immediately after taking CSn low.

Copyright © 2006–2015, Texas Instruments Incorporated

Detailed Description

13

Product Folder Links:

Summary of Contents for CC1150

Page 61: ...PACKAGE OPTION ADDENDUM www ti com 30 May 2018 Addendum Page 2 ...

Page 64: ......

Page 65: ......