Do not use the Trigger Update mode if DAC_OUT is enabled. This will cause the sequencer to lock.

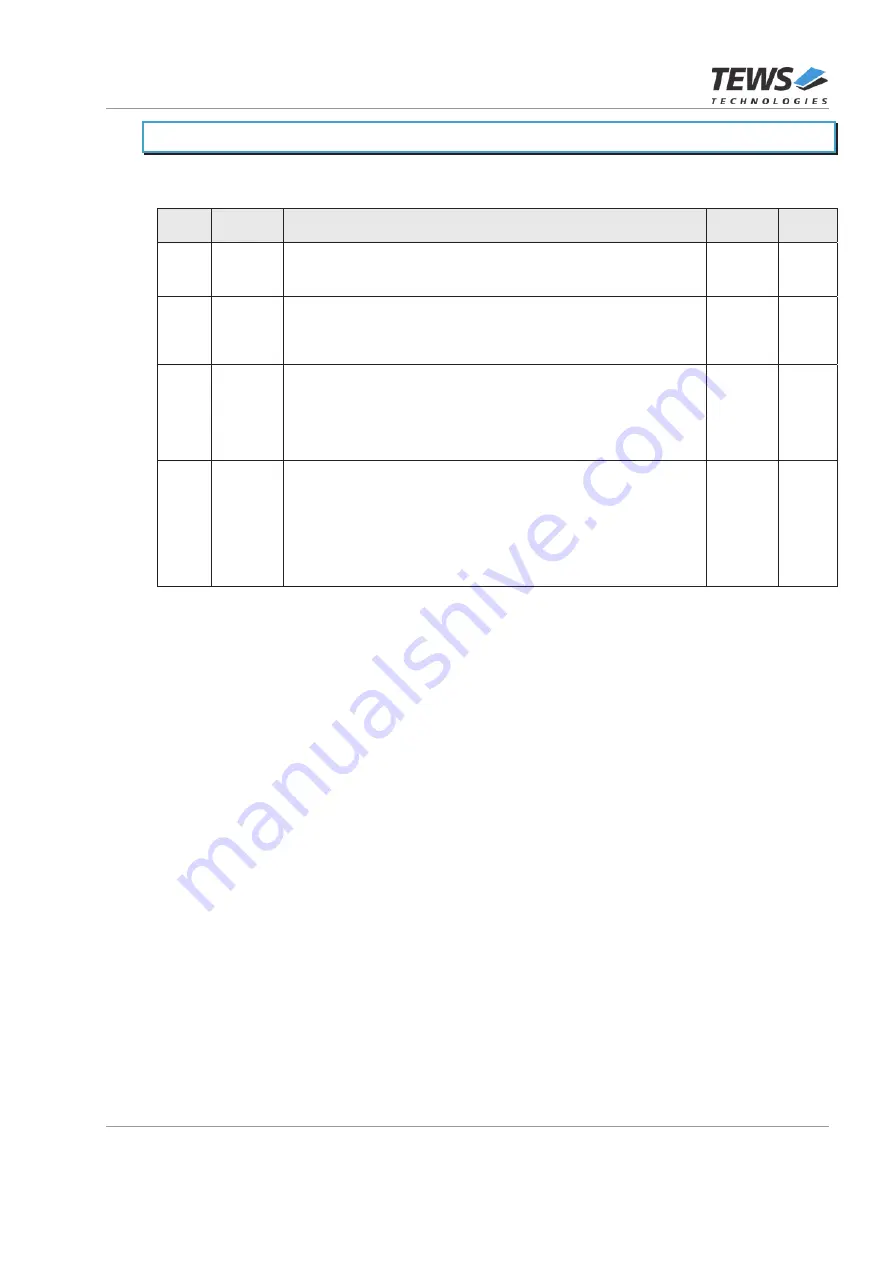

3.2.2.2 DAC Sequencer Status Register DACSEQSTAT (Offset 0x00C4)

Bit

Symbol

Description

Access

Reset

Value

31:3

-

Reserved

Write: don't care

Read: always reads as '0'

R

0

2

DAC IRQ

Pending DAC Interrupts (Read),

On a read-access this bit shows a pending DAC interrupt. Pending

interrupts are marked with a '1'.

An interrupt is acknowledged when the SDR bit is cleared.

R

0

1

SDU

Sequencer Data Underflow (bit is used to signalize a data underflow

condition for the sequencer data RAM)

1 = Sequencer Data Underflow (sequencer is ready for the next

sequence but the user has not yet confirmed new data in sequencer

data RAM).

0 = All DAC Data Registers have been updated with new data.

R

1

0

SDR

Sequencer Data Request/Acknowledge (bit is used to signalize data

request for the sequencer data RAM)

1 = Sequencer Data Request (sequencer is requesting new data in the

sequencer data RAM)

During the Simultaneous/Sequencer/Trigger Update modes this status

bit must be cleared after the sequencer data RAM has been updated

with data for the next sequence.

The bit is cleared by writing a '1'.

R/C

0

Table 3-15: DAC Sequencer Status Register

TPMC851 User Manual Issue 1.0.9

Page 25 of 65