2-21

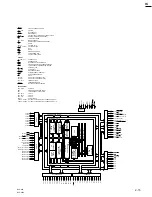

BVP-900

BVP-900P

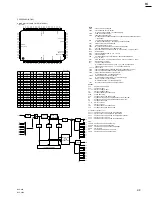

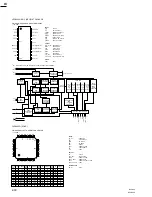

IC

1

2

3

4

5

6

7

8

PCP

(PHASE COMPARATOR) OUT

PC

1

(PHASE COMPARATOR) OUT

PC

B

(PHASE COMPARATOR) IN

VCO

(VOLTAGE CONTROLLED OSC) OUT

INH

(INHIBIT) IN

—TOP VIEW—

16

15

14

13

12

11

10

9

GND

Z

D

(ZENER) OUT

PC

A

(PHASE COMPARATOR) IN

PC

2

(PHASE COMPARATOR) OUT

SF

(SOURCE FOLLOWER) OUT

VCO

(VOLTAGE CONTROLLED OSC) IN

*

1

V

DD

2

13

1

4

6

7

10

15

PC1

PC2

PCP

VCO

OUT

C1A

C1B

SF

ZD

C-MOS PHASE LOCKED LOOP

14

3

9

11

12

5

PCA

PCB

VCO

IN

R1

R2

INH

C1

A

C1

B

R

2

R

1

SELF

BIAS

CIRCUIT

PHASE

COMPARATOR 1

PHASE

COMPARATOR 2

VCO

SOURCE

FOLLOWER

14

PCA

3

PCB

9

VCO

5

INH

GND

15

ZD

10

SF

7

C1B

6

C1A

12

R2

11

R1

4

VCO

1

PCP

13

PC2

2

PC1

TYPE

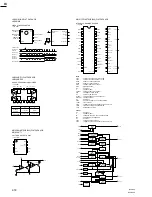

CD4046BE

HD14046BP

MC14046BCP

MC14046BF

TC4046BP

CD74HC4046AM

MC74HC4046AF

MC74HC4046AN

V

DD

+

3 to

+

8V

+

2 to

+

6V

*

1

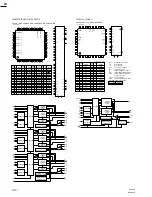

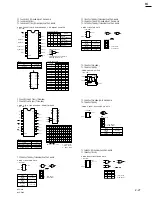

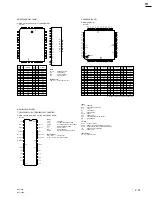

C-MOS 14-STAG RIPPLE-CARRY BINARY COUNTER/DRIVER

0

1

2

3

4

16380

16381

16382

16383

Q13

0

0

0

0

0

1

1

1

1

Q12

0

0

0

0

0

1

1

1

1

0000

0001

0002

0003

0004

4FFC

4FFD

4FFE

4FFF

*

V

DD

OUT

OUT

OUT

OUT

OUT

OUT

OUT

COUNT

BINARY OUTPUTS

1

2

3

4

5

6

7

Q11

Q12

Q13

Q5

Q4

Q6

Q3

Q10

Q9

Q7

Q8

Q0

R

D

R

D

CK

8

10

11

12

13

14

15

16

9

0 ; LOW LEVEL

1 ; HIGH LEVEL

CK

Q0

Q3

11

10

H

H

K R

D

R

D

R

D

R

D

R

D

J

Q

Q

Q

Q

Q

Q

R

D

IN HEXADECIMAL

IN DECIMAL

GND

OUT

10

11

9

7

5

4

6

13

12

14

15

1

2

3

Q0

Q3

Q4

Q5

Q6

Q7

Q8

Q9

Q10

Q11

Q12

Q13

OUT

OUT

OUT

IN

IN

OUT

Q11

0

0

0

0

0

1

1

1

1

Q10

0

0

0

0

0

1

1

1

1

Q9

0

0

0

0

0

1

1

1

1

Q8

0

0

0

0

0

1

1

1

1

Q7

0

0

0

0

0

1

1

1

1

Q6

0

0

0

0

0

1

1

1

1

Q5

0

0

0

0

0

1

1

1

1

Q4

0

0

0

0

0

1

1

1

1

Q3

0

0

0

0

0

1

1

1

1

Q0

0

1

0

1

0

0

1

0

1

TYPE

HC4020

14020, 4020, 84020

*

+

2 to

+

6V

+

3 to

+

18V

V

DD

RD

1

0

ALL LOW

COUNT

Q13-Q0

•••

•••

•••

•••

•••

•••

•••

•••

•••

•••

•••

•••

•••

•••

9

H

H

K

J

H

H

K

J

H

H

K

J

H

H

K

J

H

H

K

J

7

Q12

Q13

2

3

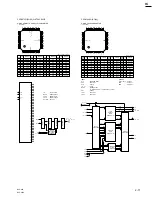

—TOP VIEW—

1

2

3

4

5

6

7

8

CK2

(CLOCK)

D2 +4

D1 +3

D1 +2

D1 +1

RD1

D1

—TOP VIEW—

16

15

14

13

12

11

10

9

GND

D2

RD2

D2 +1

D2 +2

D2 +3

D1 +4

CK1

(CLOCK)

V

DD

(

+

3 to

+

18V)

C-MOS DUAL 4-STAGE STATIC SHIFT REGISTER WITH DIRECT RESET

D

+

1

D

+

2

D

+

3

D

+

4

5

4

3

10

R

D

6

7

9

D

D

+

1

D

+

2

D

+

3

D

+

4

13

12

11

2

R

D

14

15

1

D

7

D1

D

5

D1

+

1

Q

Q

R

D

D

4

D1

+

2

Q

Q

R

D

D

3

D1

+

3

Q

Q

R

D

D

10

Q

Q

R

D

D1

+

4

9

CK1

6

R

D

1

15

D2

D

13

D2

+

1

Q

Q

R

D

D

12

D2

+

2

Q

Q

R

D

D

11

D2

+

3

Q

Q

R

D

D

2

Q

Q

R

D

D2

+

4

1

CK2

14

R

D

2

MC14015BF (MOTOROLA)FLAT PACKAGE

MC14015BFEL

MC14020BFEL (MOTOROLA)FLAT PACKAGE

MC14046BF (MOTOROLA)FLAT PACKAGE

MC14046BF-T2

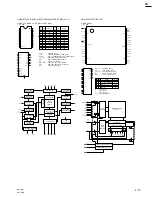

MN6790S (MATSUSHITA)

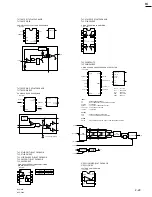

C-MOS CLOCK GENERATOR

—TOP VIEW—

PC

OUT

PC1

IN

PC2

IN

DIV

OUT

MOD2

IN

4

5

14

PC1

PC2

VCO1

2

11

6

8

PC

TEST2

DIV

1

2

3

4

5

6

7

14

13

12

11

10

9

8

A-GND

VCO1

IN

TEST2

OUT

TEST1

IN

MOD1

IN

CK

OUT

D-GND

PHASE

COMPARATOR

PC1

4

PC2

5

2

PC

VCO

14

VCO1

TEST2

11

1/684,

1/858,

1/864

DIV

6

1/2

CK

8

MOD2

FREQUENCY

RATIO

MOD1

0

1

: LOW LEVEL

: HIGH LEVEL

1/684

1/858

1/864

—

0

0

1

1

0

1

0

1

VCO

OSCILLATION

NOTE

—

STANDSTILL

CK=DIV=L

D-V

DD

(

+

4.5 to

+

5.5 V)

A-V

DD

(

+

4.5 to

+

5.5 V)

Summary of Contents for BVP-900 Series

Page 4: ......

Page 30: ......

Page 36: ......

Page 160: ......

Page 167: ......

Page 181: ......

Page 193: ......

Page 224: ......

Page 272: ......

Page 275: ......

Page 278: ......

Page 282: ......

Page 363: ......

Page 384: ......

Page 396: ......

Page 404: ......

Page 408: ......

Page 411: ......

Page 412: ......

Page 414: ......

Page 454: ......

Page 455: ......

Page 479: ......

Page 480: ......

Page 482: ......

Page 498: ......

Page 519: ......

Page 520: ......