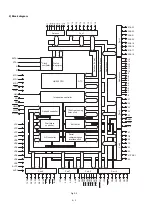

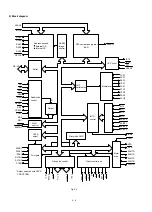

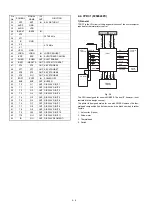

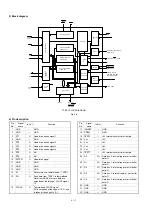

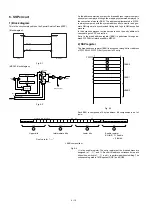

2) Block diagram

Fig. 2-4

MTD

MTD

RJMTR

SLMTD

SLMTS

SLMTR

SLMTD

TXDI

SCKI

RXDI

HTS1

SCK1

STH1

HTS2

SCK2

STH2

ROS1

ROS2

RAS1

RAS2

RAS3

OPTCS

AS

RD

WR

RDO

WRO

Φ

RESET

RES

VRESC

POFF

MD0

MD1

WAIT

RJRST

SLRST

*PRST

RJTMG

SLTMG

PTMG

INT4

INT1

INT2

INT3

EXINT0

EXINT1

EXINT2

EXINT3

SD

T1

~7

DT

1

~

9

TEST

IRQ0

A23~A0

SSPRQ

SL

F

SL

R

S

VF

RF

JF

F

CUT

PC

U

T

STAM

P

TR

G

I

TR

G

TR

G

DO

T

E

N

IRLON

D0~D7

Φ

Address decode

External CS

Internal CS

RASEL

Image

control

SSP comparison register

BAR.

Buffer

Read/write

control

Divider

CHS

serial select

Multiplexer

WAIT

control

CAPS

select

Print gate

Print pulse control

Print mode PMD

INTO

control

Printer control port

Motor

drive

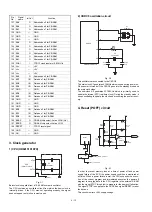

* Output selection with CAPS.

PRST/PTMG.

EXWAIT

I/R Control

IRTX

IRRX

RCI

ASKRX

4 – 6

Summary of Contents for ER-A450

Page 51: ...MAIN PWB LAYOUT 1 SIDE A 8 15 ...

Page 52: ... 2 SIDE B 8 16 ...

Page 53: ...PS PWB FRONT DISPLAY PWB POP UP DISPLAY PWB 8 17 ...