57

57

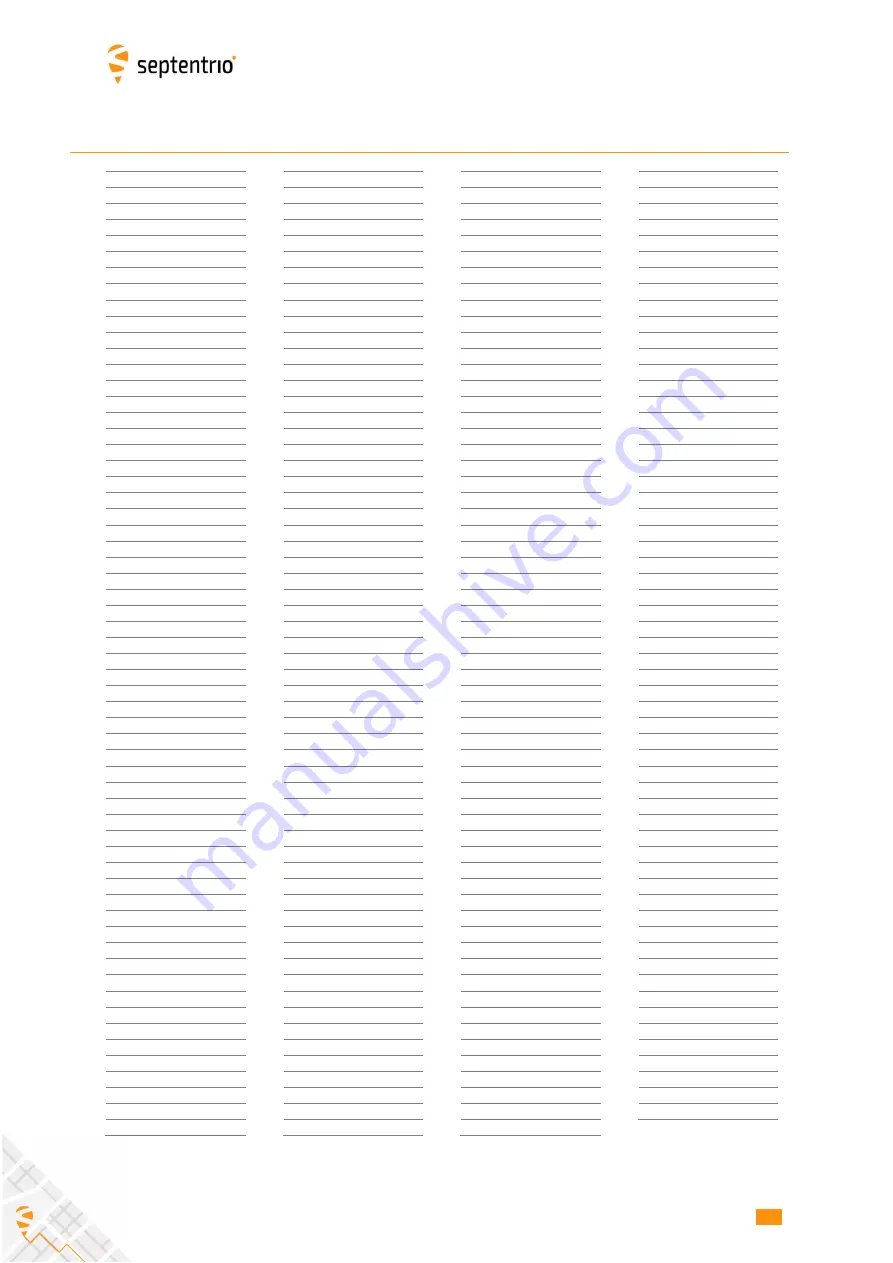

Pad List

57

Appendix E

Pad List

A2

RTC_XTALO

A3

RTC_XTALI

A4

GND

A5

USB_DEV_P

A6

USB_DEV_N

A7

GND

A8

USB_VBUS1

A9

Reserved_NC

A10

ONOFF

A11

nRST_IN

A12

MODULE_RDY

A13

Reserved_NC

A14

GPLED

A15

GND

A16

GND

A17

GND

A18

VDD_3V3

A19

VDD_3V3

A20

VDD_3V3

A21

GND

A22

GND

A23

GND

B1

RXD1

B2

LOGLED

B3

Reserved_NC

B4

GND

B5

GND

B6

GND

B7

GND

B8

VDD_BAT

B9

Reserved_NC

B10

Reserved_NC

B11

Reserved_NC

B12

Reserved_NC

B13

GND

B14

Reserved_NC

B15

Reserved_NC

B16

PMIC_ON_REQ

B17

GND

B18

VDD_3V3

B19

VDD_3V3

B20

VDD_3V3

B21

GND

B22

Reserved_NC

B23

Reserved_NC

C1

RTS1

C2

Reserved_NC

C3

Reserved_NC

C4

GND

C5

Reserved_NC

C6

Reserved_NC

C7

GND

C8

Reserved_NC

C9

Reserved_NC

C10

Reserved_NC

C11

Reserved_NC

C12

Reserved_NC

C13

Reserved_NC

C14

Reserved_NC

C15

GND

C16

GND

C17

GND

C18

VDD_3V3

C19

VDD_3V3

C20

VDD_3V3

C21

Reserved_NC

C22

Reserved_NC

C23

GND

D1

TXD1

D2

GND

D3

RXD4

D21

GND

D22

GND

D23

GND

E1

CTS1

E2

GND

E3

TXD4

E21

GND

E22

GND

E23

GND

F1

RXD2

F2

nRST_LAN

F3

Reserved_NC

F21

GND

F22

GND

F23

GND

G1

RTS2

G2

GND

G3

Reserved_NC

G21

GND

G22

Reserved_NC

G23

GND

H1

TXD2

H2

RMII_TX1

H3

Reserved_NC

H21

GND

H22

GND

H23

GND

J1

CTS2

J2

RMII_TX0

J3

Reserved_NC

J21

GND

J22

GND

J23

GND

K1

RXD3

K2

GND

K3

LOGBUTTON

K21

GND

K22

GND

K23

GND

L1

RTS3

L2

RMII_TXEN

L3

GP2

L21

GND

L22

GND

L23

GND

M1

TXD3

M2

RMII_RXER

M3

GPLED2

M21

GND

M22

GND

M23

2V8_IN

N1

CTS3

N2

RMII_CRSDV

N3

Reserved_NC

N21

GND

N22

GND

N23

2V8_OUT

P1

GND

P2

GND

P3

GND

P21

GND

P22

GND

P23

VANT

R1

Reserved_NC

R2

RMII_RXD0

R3

GND

R21

GND

R22

GND

R23

VANT

T1

Reserved_NC

T2

RMII_RXD1

T3

Reserved_NC

T21

GND

T22

GND

T23

GND

U1

Reserved_NC

U2

GND

U3

Reserved_NC

U21

GND

U22

GND

U23

GND

V1

Reserved_NC

V2

MDC

V3

Reserved_NC

V21

GND

V22

GND

V23

ANT_2

W1

Reserved_NC

W2

MDIO

W3

Reserved_NC

W21

GND

W22

GND

W23

GND

Y1

SD1_DATA0

Y2

GND

Y3

Reserved_NC

Y21

GND

Y22

GND

Y23

GND

AA1

SD1_CLK

AA2

RMII_CLK

AA3

Reserved_NC

AA4

GP1

AA5

Reserved_NC

AA6

Reserved_NC

AA7

Reserved_NC

AA8

Reserved_NC

AA9

Reserved_NC

AA10

Reserved_NC

AA11

Reserved_NC

AA12

Reserved_NC

AA13

GND

AA14

GND

AA15

GND

AA16

GND

AA17

GND

AA18

GND

AA19

GND

AA20

GND

AA21

GND

AA22

GND

AA23

GND

AB1

SD1_CMD

AB2

GND

AB3

GND

AB4

GND

AB5

GND

AB6

GND

AB7

Reserved_GND

AB8

GND

AB9

Reserved_NC

AB10

Reserved_NC

AB11

Reserved_NC

AB12

Reserved_NC

AB13

GND

AB14

GND

AB15

GND

AB16

GND

AB17

GND

AB18

GND

AB19

GND

AB20

GND

AB21

GND

AB22

GND

AB23

GND

AC1

Reserved_NC

AC2

Reserved_NC

AC3

SYNC

AC4

1V8_OUT

AC5

Reserved_NC

AC6

EVENTA

AC7

EVENTB

AC8

PPSO

AC9

Reserved_NC

AC10

Reserved_NC

AC11

Reserved_NC

AC12

Reserved_NC

AC13

GND

AC14

VTUNE

AC15

GND

AC16

REF_O

AC17

REF_I

AC18

GND

AC19

GND

AC20

ANT_1

AC21

GND

AC22

GND

AC23

GND