5.

System Diagram

5. System Diagram

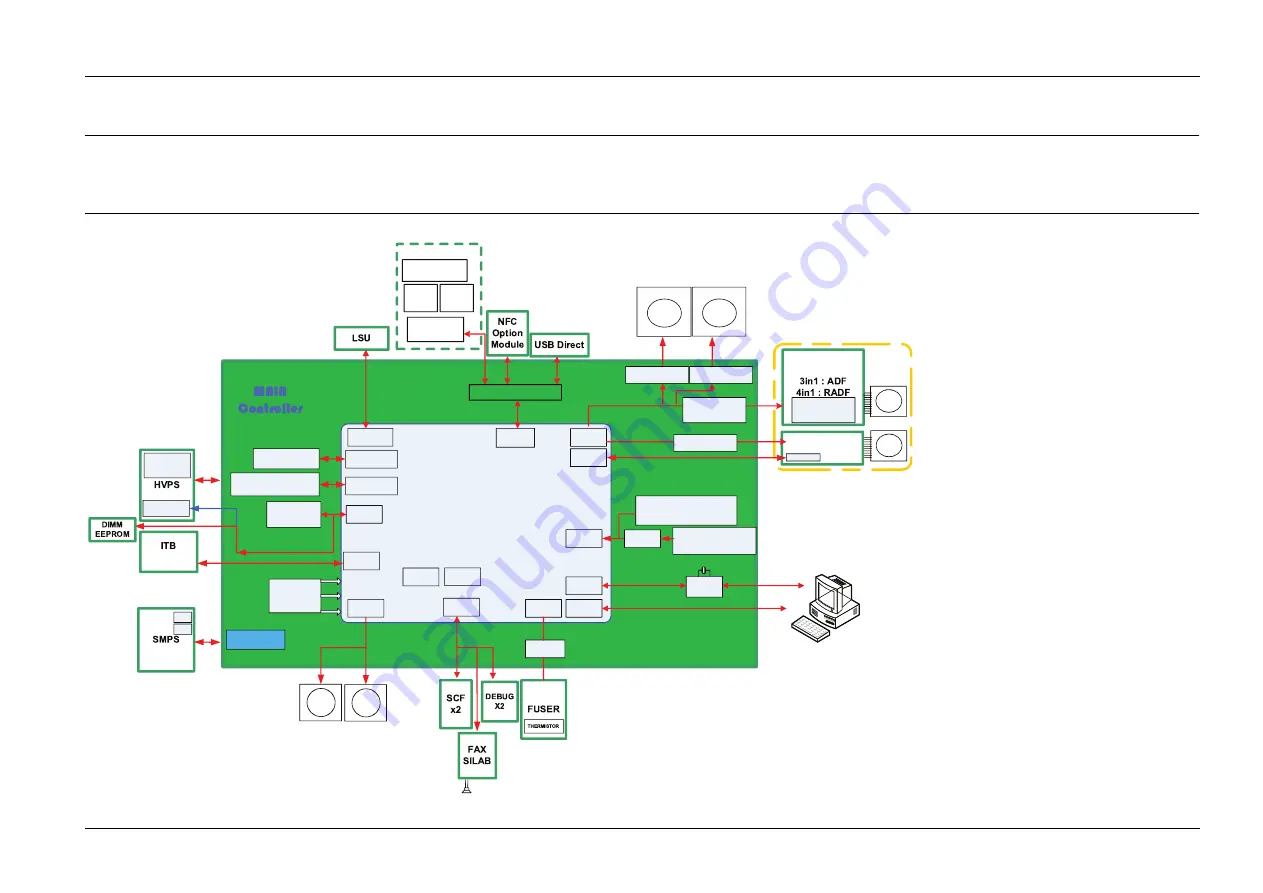

5.1. Block Diagram

S C A N

A 2000

C ore :

800M Hz

/

400M Hz

SY STEM :

200M Hz

D D R :800M Hz

C ort

ex-A 9 /

C ort

ex-R 4

N AN D Flash

(O S )

128M B

O PE

4.3" TS P

TO U C H LC D

O P E M IC O M

N X P2120

SP EA K ER

N ET W O R K

R TL 8211E -V L-C G T

25M Hz

D DR 3

C O N TR O LLER

U SB

D EVIC E

U SB

H O ST

I2C X

3

M A C

FUSER

FEED

M otor

M T

STEP

FUSER

M otor

M T

STEP

U AR T X

5

LSU

C ontroller

G PIO

C lock

G enerator

A SM 3P2863A

V C L K

U S B

C L K

M C L K

M T

B LD C

K

M otor

M T

B LD C

YM C

M otor

U S B H U B

STEP

M O TO R

B LD C

M O TO R

M T

ST EP

D DR 3 SO D IM M

256M B (C 3010, C 3060 3in1)

512M B (C 3060 4in1)

EEPR O M

M 24512

X 1EA

64K B

N AN D FLA SH

A CR U M

(Y, M , C , K )

SC A N I/F

A CR ,

C TD

A DC

PW M

D CIS

24V

5V

M H V, THV,

D EV_D C _FU

SER _B IAS

M U X

TH V1_R EA D ,

TH V2_R EA D ,

I

N N ER _TEM P,

TEM P_LSU 1,

A D C_C TD _C A L_LEFT,

A M B I

E N T,

H U M I

D I

TY ,

W AS TE_R X

A D C_C TDP ,A D C_C TDS ,N C TH _C ,

N C TH _D ,

A D C_A C R_LEFT.

A D C_A C R_R I

G H T,

A D C_C TD _C A L_R I

G H T

256M B

N A N D

256M B

D D R 2

3C H D C DC

(1.5V, 1.2V, 3.3V)

A TTINY 25

STEP

A 4984

Q FN

M T

ST EP

STEP

A 4984

Q FN

STEP

A 4984

Q FN

STEP

A 4984

Q FN

A DF O N LY

STEP

A 4984

Q FN

R AD F O N LY

Copyright© 1995-2017 SAMSUNG. All rights reserved.

5-1