RDC

®

RISC DSP Controller

R8810LV

RDC Semiconductor Co.

Rev:1.2

Subject to change without notice

71

PIO Unit

R8810 provides 32 programmable I/O signals, which are multi-function pins with others normal function signals. Software is

programmed through the registers ( 7Ah, 78h, 76h, 74h, 72h, 70h) to configure the multi-function pins for PIO or normal

function.

PIO multi-function Pin list table

PIO No.

Pin No.

Multi Function

Reset status/PIO internal resister

0

72

TMRIN1

Input with 10k pull-up

1

73

TMROUT1

Input with 10k pull-down

2

59

6

PCS /A2

Input with 10k pull-up

3

60

5

PCS /A1

Input with 10k pull-up

4

48

DT/

R

Normal operation/ Input with 10k pull-up

5

49

DEN

Normal operation/ Input with 10k pull-up

6

46

SRDY

Normal operation/ Input with 10k pull-down

7

22

A17

Normal operation/ Input with 10k pull-up

8

20

A18

Normal operation/ Input with 10k pull-up

9

19

A19

Normal operation/ Input with 10k pull-up

10

74

TMROUT0

Input with 10k pull-down

11

75

TMRIN0

Input with 10k pull-up

12

77

DRQ0

Input with 10k pull-up

13

76

DRQ1

Input with 10k pull-up

14

50

0

MCS

Input with 10k pull-up

15

51

1

MCS

Input with 10k pull-up

16

66

0

PCS

Input with 10k pull-up

17

65

1

PCS

Input with 10k pull-up

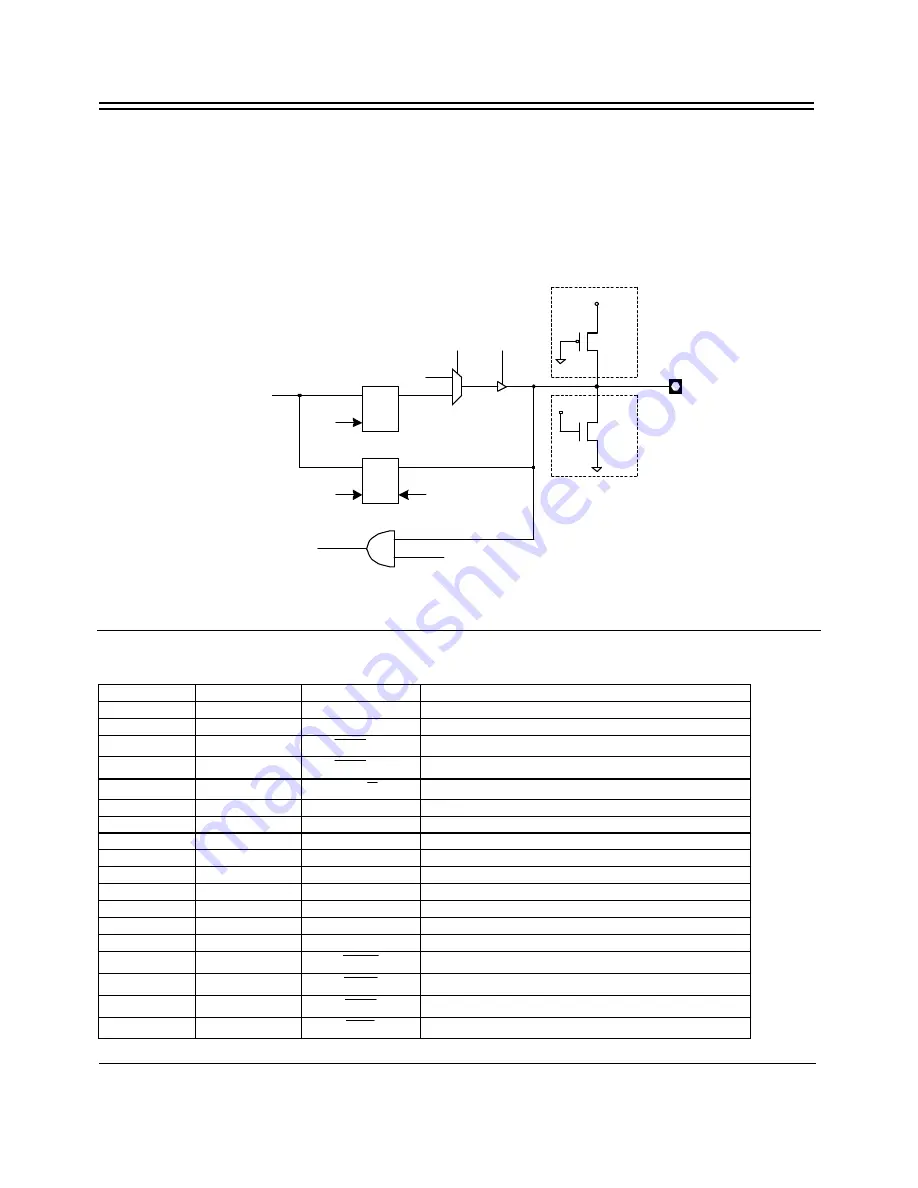

D

Q

D

Q

OE

Write

PDATA

VCC

VCC

For internal

pull-up

For internal

pull-down

Pin

"0":un-normal function

Normal Data In

Read

PDATA

Microprocessor

Clock

PIO

Direction

PIO

Mode

Normal Function

PIO Data In/Out

PIO pin Operation Diagram