16

09/18/00 Rev 1.1

12345678901234567890123456789012123456789012345678901234567890121234567890123456789012345678901212345678901234567890123456789012123456

12345678901234567890123456789012123456789012345678901234567890121234567890123456789012345678901212345678901234567890123456789012123456

PI7C7100

3-Port PCI Bridge

ADVANCE INFORMATION

n

o

i

t

c

a

s

n

a

r

T

f

o

e

p

y

T

n

o

i

t

i

d

n

o

C

y

r

a

d

n

u

o

B

s

s

e

r

d

d

A

d

e

n

g

i

l

A

e

t

i

r

w

d

e

y

a

l

e

D

ll

A

r

e

f

s

n

a

r

t

a

t

a

d

e

n

o

r

e

t

f

a

s

t

c

e

n

n

o

c

s

i

D

e

t

i

r

w

y

r

o

m

e

m

d

e

t

s

o

P

6

1

,

8

,

4

,

2

,

1

o

t

l

a

u

q

e

t

o

n

e

z

i

s

e

n

il

e

h

c

a

C

y

r

a

d

n

u

o

b

s

s

e

r

d

d

a

d

e

n

g

il

a

B

K

4

e

t

i

r

w

y

r

o

m

e

m

d

e

t

s

o

P

6

1

,

8

,

4

,

2

,

1

=

e

z

i

s

e

n

il

e

h

c

a

C

y

r

a

d

n

u

o

b

e

n

il

e

h

c

a

c

t

a

s

t

c

e

n

n

o

c

s

i

D

e

t

a

d

il

a

v

n

i

d

n

a

e

t

i

r

w

y

r

o

m

e

m

d

e

t

s

o

P

6

1

,

8

,

4

,

2

,

1

o

t

l

a

u

q

e

t

o

n

e

z

i

s

e

n

il

e

h

c

a

C

y

r

a

d

n

u

o

b

s

s

e

r

d

d

a

d

e

n

g

il

a

B

K

4

e

t

a

d

il

a

v

n

i

d

n

a

e

t

i

r

w

y

r

o

m

e

m

d

e

t

s

o

P

6

1

,

8

,

4

,

2

,

1

=

e

z

i

s

e

n

il

e

h

c

a

C

,

y

r

a

d

n

u

o

b

e

n

il

e

h

c

a

C

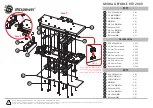

Table 4-3. Write Transaction Disconnect Address Boundaries

Note 1. Memory-write-disconnect-control bit is bit 1 of the chip control register at offset 40h in configuration space.

4.5.5 Buffering Multiple Write Transactions

PI7C7100 continues to accept posted memory write transactions as long as space for at least one DWORD of data in

the posted write data buffer remains. If the posted write data buffer fills before the initiator terminates the write transaction,

PI7C7100 returns a target disconnect to the initiator.

Delayed write transactions are posted as long as at least one open entry in the delayed transaction queue exists.

Therefore, several posted and delayed write transactions can exist in data buffers at the same time. See Chapter 6 for

information about how multiple posted and delayed write transactions are ordered.

4.5.6 Fast Back-to-Back Write Transactions

PI7C7100 can recognize and post fast back-to-back write transactions. When PI7C7100 cannot accept the second

transaction because of buffer space limitations, it returns a target retry to the initiator.

claims the access by asserting DEVSEL# and returns TRDY# to the initiator, to indicate that the write data was transferred.

If the initiator requests multiple DWORD, PI7C7100 also asserts STOP# in conjunction with TRDY# to signal a target

disconnect. Note that only those bytes of write data with valid byte enable bits are compared. If any of the byte enable

bits are turned off (driven HIGH), the corresponding byte of write data is not compared.

If the initiator repeats the write transaction before the data has been transferred to the target, PI7C7100 returns a target

retry to the initiator. PI7C7100 continues to return a target retry to the initiator until write data is delivered to the target,

or until an error condition is encountered. When the write transaction is repeated, PI7C7100 does not make a new entry

into the delayed transaction queue. Section 4.8.3.1 provides detailed information about how PI7C7100 responds to target

termination during delayed write transactions.

PI7C7100 implements a discard timer that starts counting when the delayed write completion is at the head of the delayed

transaction queue. The initial value of this timer can be set to the retry counter register offset 78h. If the initiator does not

repeat the delayed write transaction before the discard timer expires, PI7C7100 discards the delayed write completion

from the delayed transaction queue. PI7C7100 also conditionally asserts P_SERR# (see Section 7.4).

4.5.4 Write Transaction Address Boundaries

PI7C7100 imposes internal address boundaries when accepting write data. The aligned address boundaries are used to

prevent PI7C7100 from continuing a transaction over a device address boundary and to provide an upper limit on maximum

latency. PI7C7100 returns a target disconnect to the initiator when it reaches the aligned address boundaries under conditions

shown in Table 4–3.