2-86

Computer Group Literature Center Web Site

Hawk PCI Host Bridge & Multi-Processor Interrupt Controller

2

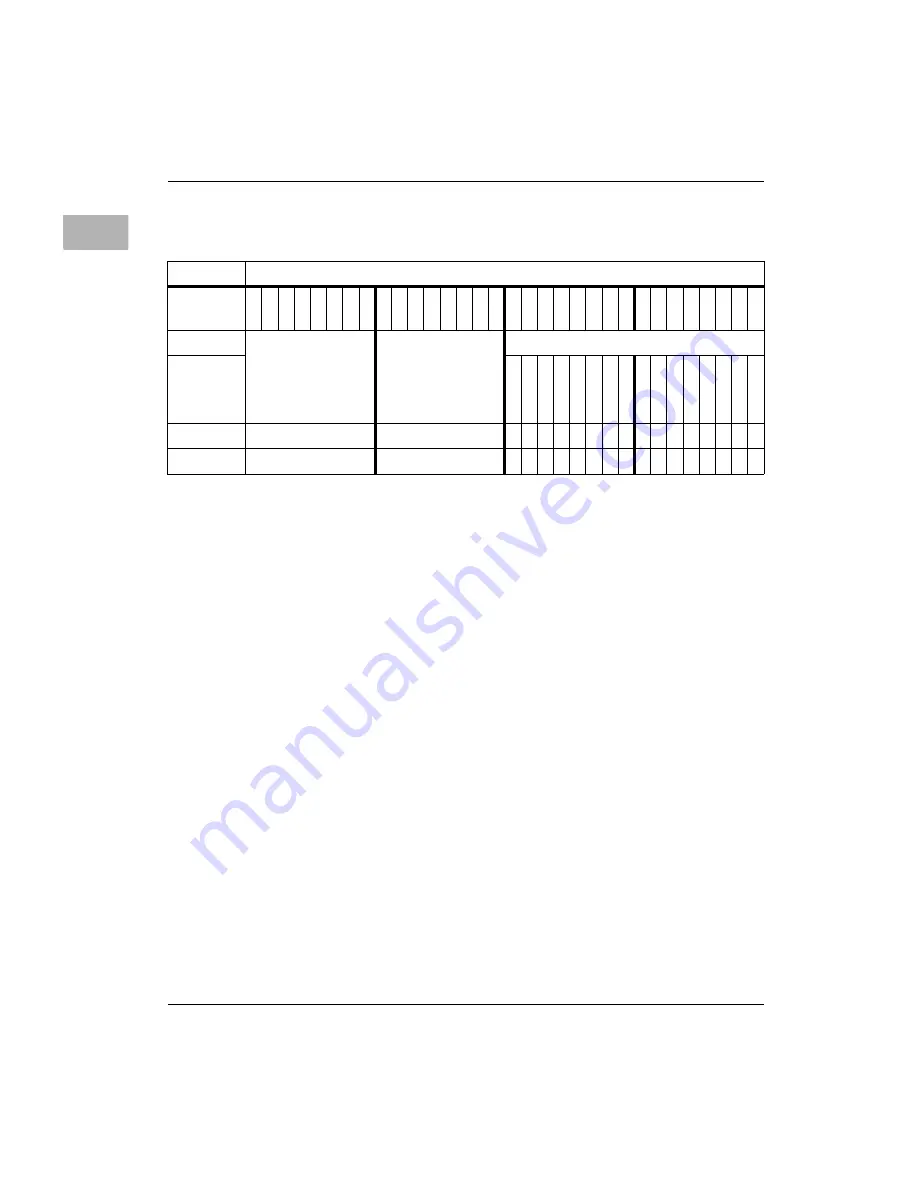

If the PSMA or PRTA bit are set, the register is defined by the following

table:

WP

Write Post Completion. This bit is set when the PCI

master detects an error while completing a write post

transfer.

XIDx

PPC Master ID. This field contains the ID of the PPC

master which originated the transfer in which the error

occurred. The encoding scheme is identical to that used in

the GCSR register.

COMMx

PCI Command. This field contains the PCI command of

the PCI transfer in which the error occurred.

BYTEx

PCI Byte Enable. This field contains the PCI byte enables

of the PCI transfer in which the error occurred. A set bit

designates a selected byte.

Address

$FEFF002C

Bit

0 1 2 3 4 5 6 7 8 9

1

0

1

1

1

2

1

3

1

4

1

5

1

6

1

7

1

8

1

9

2

0

2

1

2

2

2

3

2

4

2

5

2

6

2

7

2

8

2

9

3

0

3

1

Name

EATTR

WP

MID1

MID0

COMM3

COMM2

COMM1

COMM0

BYTE7

BYTE6

BYTE5

BYTE4

BYTE3

BYTE2

BYTE1

BYTE0

Operation

R

R

R

R

R

R

R

R

R

R

R

R

R

R

R

R

R

R

Reset

$00

$00

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Summary of Contents for MVME5100 Series

Page 1: ...MVME5100 Single Board Computer Programmer s Reference Guide V5100A PG2 September 2001 Edition ...

Page 16: ...xvi ...

Page 20: ...xx ...

Page 28: ...xxviii ...

Page 62: ...1 34 Computer Group Literature Center Web Site Product Data and Memory Maps 1 ...

Page 278: ...3 88 Computer Group Literature Center Web Site System Memory Controller SMC 3 ...

Page 288: ...4 10 Computer Group Literature Center Web Site Hawk Programming Details 4 ...

Page 320: ...Index IN 12 Computer Group Literature Center Web Site I N D E X ...