Registers

http://www.motorola.com/computer/literature

2-89

2

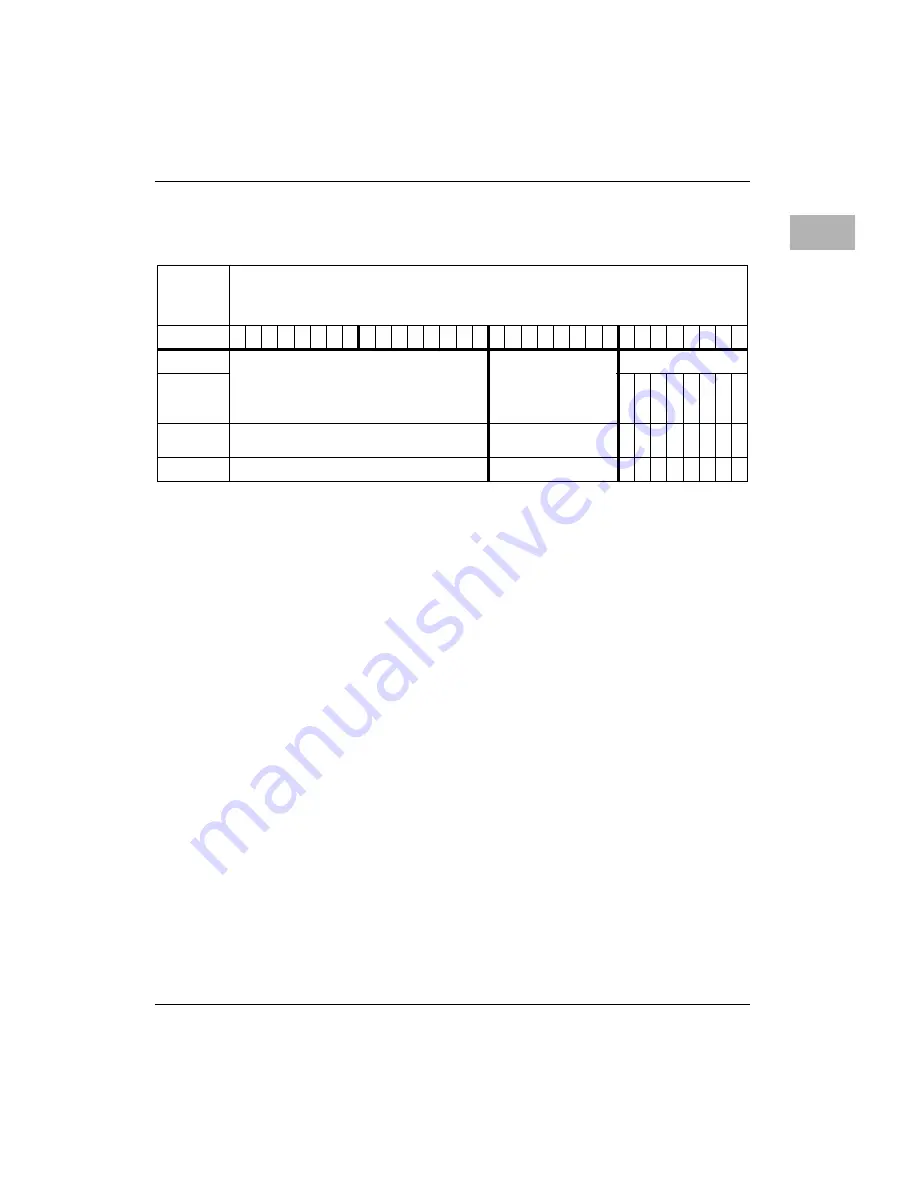

PPC Slave Offset/Attribute (0, 1 and 2) Registers

The PPC Slave Offset Registers (XSOFF0, XSOFF1, and XSOFF2)

contains offset information associated with the mapping of PPC memory

space to PCI memory I/O space. The field within the XSOFFx registers is

defined as follows:

XSOFFx

PPC Slave Offset. This register contains a 16-bit offset

that is added to the upper 16 bits of the PPC address to

determine the PCI address used for transfers from the PPC

bus to PCI. This offset allows PCI resources to reside at

addresses that would not normally be visible from the

PPC bus.

The PPC Slave Attributes Registers (XSATT0, XSATT1, and XSATT2)

contain attribute information associated with the mapping of PPC memory

space to PCI memory I/O space. The bits within the XSATTx registers are

defined as follows:

REN

Read Enable. If set, the corresponding PPC Slave is

enabled for read transactions.

WEN

Write Enable. If set, the corresponding PPC Slave is

enabled for write transactions.

WPEN

Write Post Enable. If set, write posting is enable for the

corresponding PPC Slave.

Address

XSOFF0/XSATT0 - $FEFF0044

XSOFF1/XSATT1 - $FEFF004C

XSOFF2/XSATT2 - $FEFF0054

Bit

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

Name

XSOFFx

XSATTx

REN

WE

N

WP

EN

MEM

IO

M

Operation

R/W

R

R/W

R/W

R

R/W

R

R

R/W

R/W

Reset

$0000

$00

0

0

0

0

0

0

0

0

Summary of Contents for MVME5100 Series

Page 1: ...MVME5100 Single Board Computer Programmer s Reference Guide V5100A PG2 September 2001 Edition ...

Page 16: ...xvi ...

Page 20: ...xx ...

Page 28: ...xxviii ...

Page 62: ...1 34 Computer Group Literature Center Web Site Product Data and Memory Maps 1 ...

Page 278: ...3 88 Computer Group Literature Center Web Site System Memory Controller SMC 3 ...

Page 288: ...4 10 Computer Group Literature Center Web Site Hawk Programming Details 4 ...

Page 320: ...Index IN 12 Computer Group Literature Center Web Site I N D E X ...