3-68

Computer Group Literature Center Web Site

System Memory Controller (SMC)

3

Note that RAM A/B/C/D BASE are located at $FEF80018

(refer to the section titled SDRAM Base Address Register

(Blocks A/B/C/D) for more information). They operate the

same for blocks A-D as these bits do for blocks E-H.

Also note that the combination of RAM_X_BASE and

ram_x_siz should never be programmed such that SDRAM

responds at the same address as the CSR, ROM/Flash,

External Register Set, or any other slave on the PowerPC bus.

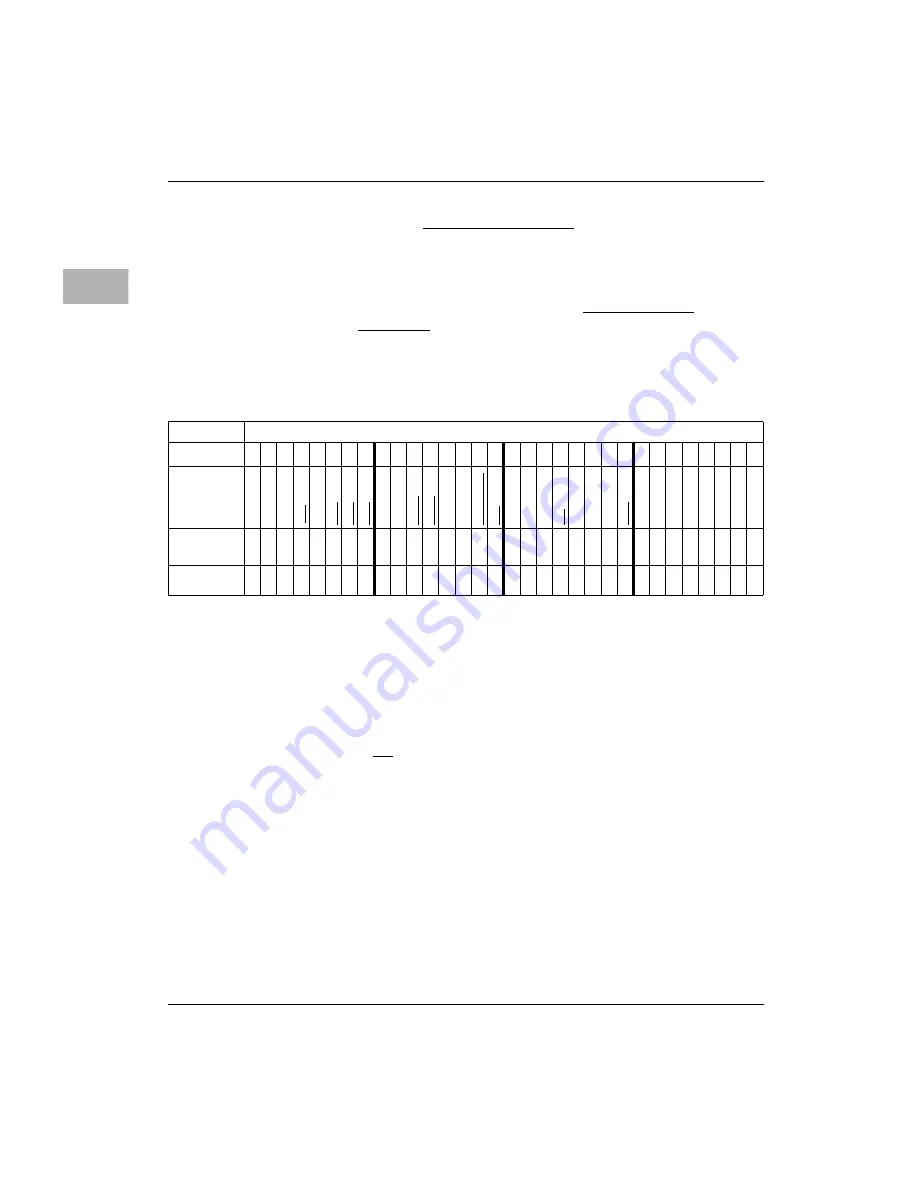

SDRAM Speed Attributes Register

The SDRAM Speed Attributes Register should be programmed based on

the SDRAM device characteristics and the Hawk’s operating frequency to

ensure reliable operation.

In order for writes to this register to work properly they should be

separated from any SDRAM accesses by a refresh before the write and by

another refresh after the write. The refreshes serve two purposes: 1) they

make sure that all of the SDRAMs are idle ensuring that mode-register-set

operations for cl3 updates work properly, and 2) they make sure that no

SDRAM accesses happen during the write. A simple way to meet these

requirments is to use the following sequence:

1. Make sure all accesses to SDRAM are done.

2. Wait for the “32-Bit Counter” (refer to section further on) to

increment at least 100 times.

3. Perform the write/writes to this register (and other SMC registers if

desired).

4. Wait again for the “32-Bit Counter” to increment at least 100 times

before resuming accesses to SDRAM.

Address

$FEF800D0

Bit

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

Name

0

0

0

cl3

0 tr

c0

tr

c1

tr

c2

0

0 tr

as

0

tr

as

1

0

0 swr_

dpl

l

td

p

0

0

0 tr

p

0

0

0 tr

cd

0

0

0

0

0

0

0

0

Operation

R

R

R

R/

W

R

R/

W

R/

W

R/

W

R

R

R/

W

R/

W

R

R

R/

W

R/

W

R

R

R

R/

W

R

R

R

R/

W

R

R

R

R

R

R

R

R

Reset

X

X

X

1 P

X

0 P

1 P

1 P

X

X

1 P

1 P

X

X

1 P

1 P

X

X

X

1 P

X

X

X

1 P

X

X

X

X

X

X

X

X

Summary of Contents for MVME5100 Series

Page 1: ...MVME5100 Single Board Computer Programmer s Reference Guide V5100A PG2 September 2001 Edition ...

Page 16: ...xvi ...

Page 20: ...xx ...

Page 28: ...xxviii ...

Page 62: ...1 34 Computer Group Literature Center Web Site Product Data and Memory Maps 1 ...

Page 278: ...3 88 Computer Group Literature Center Web Site System Memory Controller SMC 3 ...

Page 288: ...4 10 Computer Group Literature Center Web Site Hawk Programming Details 4 ...

Page 320: ...Index IN 12 Computer Group Literature Center Web Site I N D E X ...