Registers

http://www.motorola.com/computer/literature

2-115

2

M

CASCADE MODE. Allows cascading of an external

8259 pair connected to the first interrupt source input pin

(0). In the pass through mode, interrupt source 0 is passed

directly through to the processor 0 INT pin. MPIC is

essentially disabled. In the mixed mode, 8259 interrupts

are delivered using the priority and distribution

mechanism of the MPIC. The Vector/Priority and

Destination registers for interrupt source 0 are used to

control the delivery mode for all 8259 generated interrupt

sources.

TIE

Tie Mode. Writing a one to this register bit will cause a tie

in external interrupt processing to swap back and forth

between processor 0 and 1. The first tie in external

interrupt processing always goes to Processor 0 after a

reset. When this register bit is set to 0, a tie in external

interrupt processing will always go to processor 0 (Mode

used on Version $02 of MPIC).

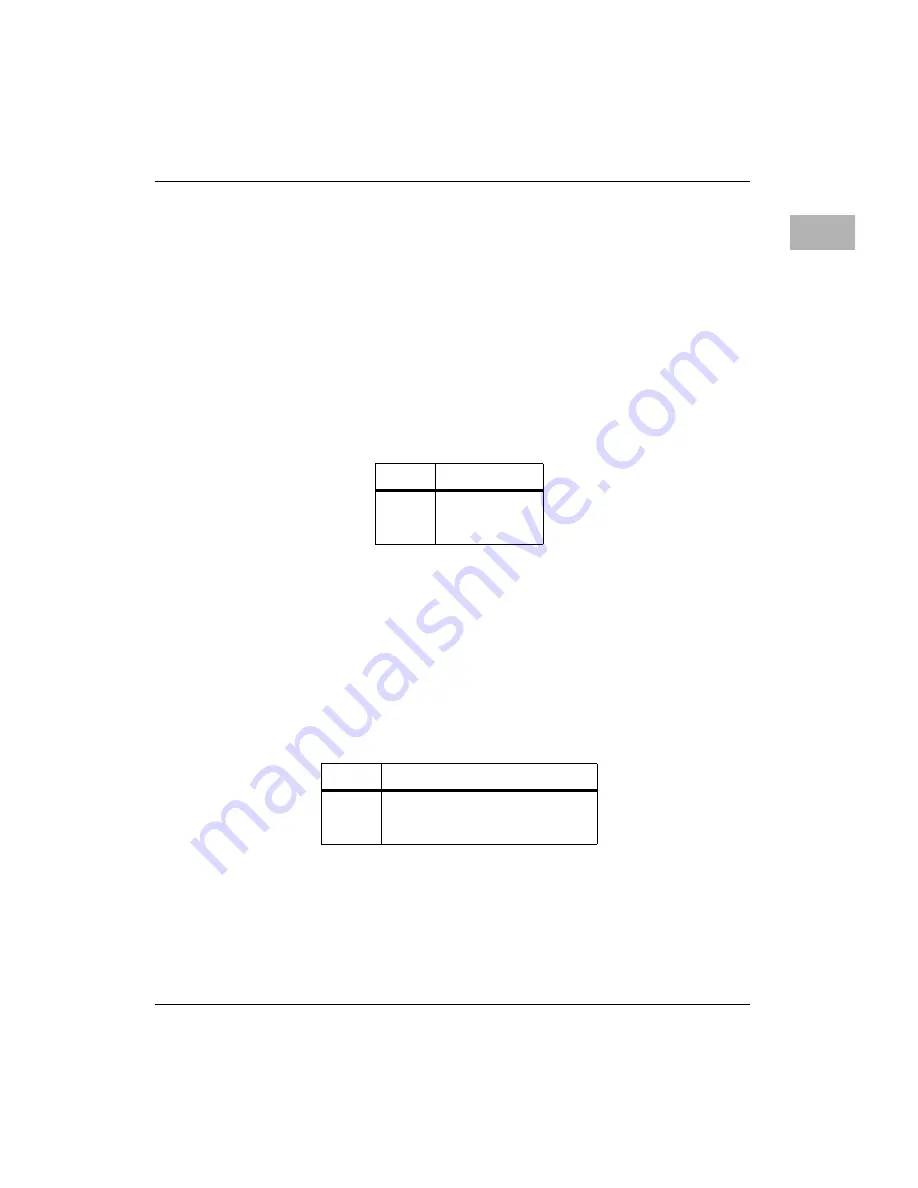

Table 2-20. Cascade Mode Encoding

M

Mode

0

Pass Through

1

Mixed

Table 2-21. Tie Mode Encoding

T

Mode

0

Processor 0 always selected

1

Swap between Processor’s

Summary of Contents for MVME5100 Series

Page 1: ...MVME5100 Single Board Computer Programmer s Reference Guide V5100A PG2 September 2001 Edition ...

Page 16: ...xvi ...

Page 20: ...xx ...

Page 28: ...xxviii ...

Page 62: ...1 34 Computer Group Literature Center Web Site Product Data and Memory Maps 1 ...

Page 278: ...3 88 Computer Group Literature Center Web Site System Memory Controller SMC 3 ...

Page 288: ...4 10 Computer Group Literature Center Web Site Hawk Programming Details 4 ...

Page 320: ...Index IN 12 Computer Group Literature Center Web Site I N D E X ...