2-124

Computer Group Literature Center Web Site

Hawk PCI Host Bridge & Multi-Processor Interrupt Controller

2

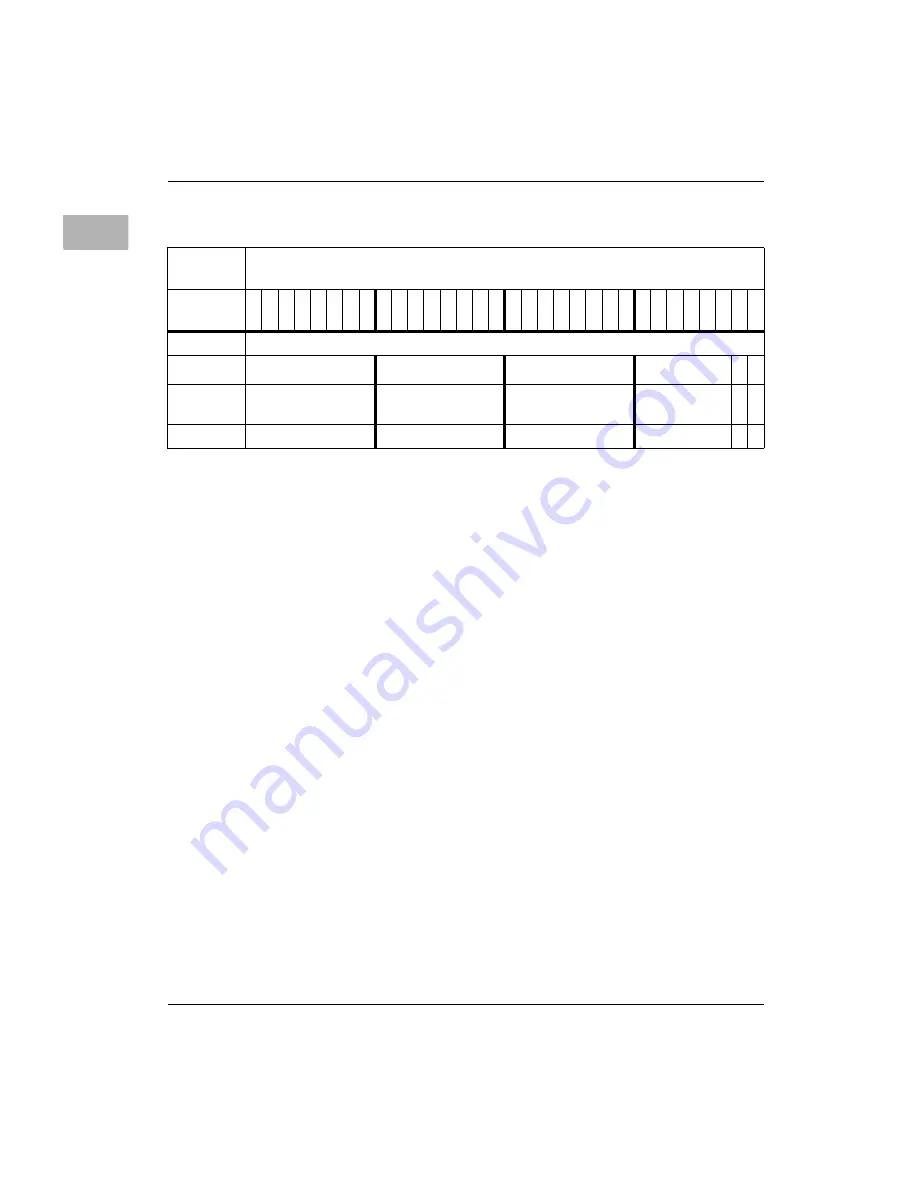

External Source Destination Registers

This register indicates the possible destinations for the external interrupt

sources. These interrupts operate in the Distributed interrupt delivery

mode.

P1

PROCESSOR 1. The interrupt is pointed to processor 1.

P0

PROCESSOR 0. The interrupt is pointed to processor 0.

Offset

Int Src 0 - $10010

Int Src 1-> Int Src 15 - $10030 -> $101F0

Bit

3

1

3

0

2

9

2

8

2

7

2

6

2

5

2

4

2

3

2

2

2

1

2

0

1

9

1

8

1

7

1

6

1

5

1

4

1

3

1

2

1

1

1

0 9 8 7 6 5 4 3 2 1 0

Name

EXTERNAL SOURCE DESTINATION

P1

P0

Operation

R

R

R

R

R/

W

R/W

Reset

$00

$00

$00

$00

0

0

Summary of Contents for MVME5100 Series

Page 1: ...MVME5100 Single Board Computer Programmer s Reference Guide V5100A PG2 September 2001 Edition ...

Page 16: ...xvi ...

Page 20: ...xx ...

Page 28: ...xxviii ...

Page 62: ...1 34 Computer Group Literature Center Web Site Product Data and Memory Maps 1 ...

Page 278: ...3 88 Computer Group Literature Center Web Site System Memory Controller SMC 3 ...

Page 288: ...4 10 Computer Group Literature Center Web Site Hawk Programming Details 4 ...

Page 320: ...Index IN 12 Computer Group Literature Center Web Site I N D E X ...