Integrated

Circuit

Systems, Inc.

General Description

Features

ICS1890

10Base-T/100Base-TX Integrated PHYceiver

ICS1890RevG 10/21/97

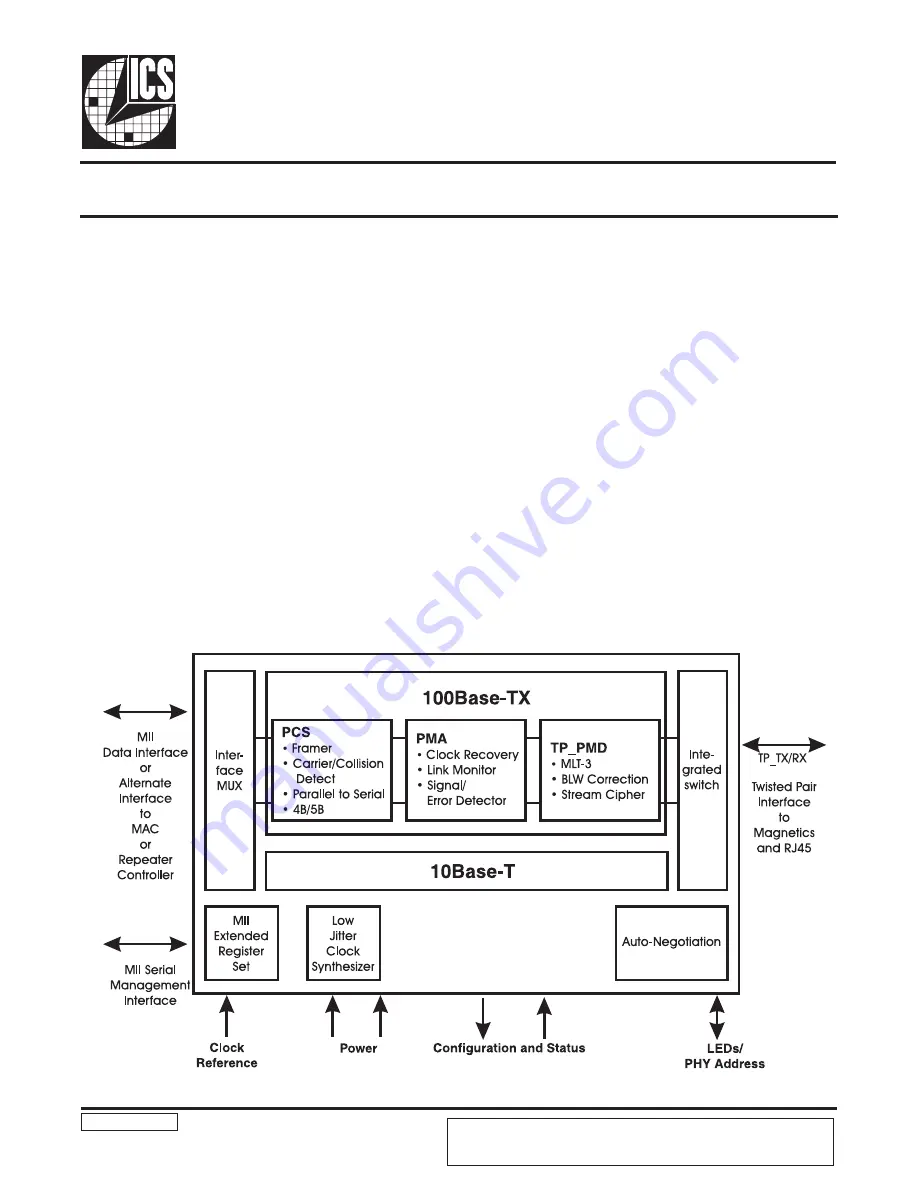

Block Diagram

One chip integrated physical layer

All CMOS, Low power design (<200mA max)

Small footprint 64-pin 14mm

2

QFP package

ISO/IEC 8802-3 CSMA/CD compliant

Media Independent Interface (MII)

Alternate 100M stream and 10M 7-wire serial

interfaces provided

10Base-TX Half & Full Duplex

100Base-TX Half & Full Duplex

Fully integrated TP-PMD including Stream

Cipher Scrambler, MLT-3 encoder, Adaptive

Equalization, and Baseline Wander Correction

Circuitry

PHYceiver and QuickPoll are trademarks of Integrated

Circuit Systems, Inc. Patents pending.

The

ICS1890

is a fully integrated physical layer device

supporting 10 and 100Mb/s CSMA/CD Ethernet applications.

DTE (adapter cards or motherboards), switching hub, repeater

and router applications are fully supported. The

ICS1890

is compliant with the ISO/IEC 8802-3 Ethernet standard

for 10 and 100Mb/s operation. A Media Independent Interface

allowing direct chip-to-chip connection, motherboard-to-

daughterboard connection or connection via an AUI-like

cable is provided. A station management interface is

provided to enable command information and status

information exchange. The

ICS1890

interfaces directly to

transmit and receive isolation transformers and can support

shielded twisted pair (STP) and unshielded twisted pair

(UTP) category 5 cables up to 105 meters. Operation in half

duplex or full duplex modes at either 10 or 100 Mbps

speeds is possible with control by Auto-Negotiation or

manual selection. By employing Auto-Negotiation the

technology capabilities of the remote link partner may be

determined and operation automatically adjusted to the

highest performance common operating mode.

ICS reserves the right to make changes in the device data identified in this publication

without further notice. ICS advises its customers to obtain the latest version of all

device data to verify that any information being relied upon by the customer is current

and accurate.

Summary of Contents for PHYceiver ICS1890

Page 49: ...49 ICS1890 Pin Configuration...