24

EPSON

S1C63656 TECHNICAL MANUAL

CHAPTER 4: PERIPHERAL CIRCUITS AND OPERATION (Memory Map)

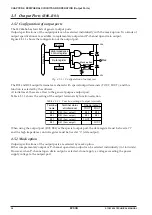

Table 4.1.1 (g) I/O memory map (FFD4H–FFF0H)

Address

Comment

D3

D2

Register

D1

D0

Name

Init

∗

1

1

0

FFE5H

EIT3

EIT2

EIT1

EIT0

R/W

EIT3

EIT2

EIT1

EIT0

0

0

0

0

Enable

Enable

Enable

Enable

Mask

Mask

Mask

Mask

Interrupt mask register (Clock timer 1 Hz)

Interrupt mask register (Clock timer 2 Hz)

Interrupt mask register (Clock timer 8 Hz)

Interrupt mask register (Clock timer 32 Hz)

FFE4H

0

0

0

EIK1

R

R/W

0

∗

3

0

∗

3

0

∗

3

EIK1

–

∗

2

–

∗

2

–

∗

2

0

Enable

Mask

Unused

Unused

Unused

Interrupt mask register (K10–K13)

FFE9H

0

0

0

EIT4

R

R/W

0

∗

3

0

∗

3

0

∗

3

EIT4

–

∗

2

–

∗

2

–

∗

2

0

Enable

Mask

Unused

Unused

Unused

Interrupt mask register (Clock timer 16 Hz)

FFE6H

EIRUN

EILAP

EISW1 EISW10

R/W

EIRUN

EILAP

EISW1

EISW10

0

0

0

0

Enable

Enable

Enable

Enable

Mask

Mask

Mask

Mask

Interrupt mask register (Stopwatch direct RUN)

Interrupt mask register (Stopwatch direct LAP)

Interrupt mask register (Stopwatch timer 1 Hz)

Interrupt mask register (Stopwatch timer 10 Hz)

FFE7H

0

0

EIRFB

EIRFM

R

R/W

0

∗

3

0

∗

3

EIRFB

EIRFM

–

∗

2

–

∗

2

0

0

Enable

Enable

Mask

Mask

Unused

Unused

Interrupt mask register (R/f converter reference oscillate completion)

Interrupt mask register (R/f converter sensor oscillate completion)

FFE8H

0

0

EISMD2 EISMD1

R

R/W

0

∗

3

0

∗

3

EISMD2

EISMD1

–

∗

2

–

∗

2

0

0

Enable

Enable

Mask

Mask

Unused

Unused

Interrupt mask register (Motor driver Ch. 2)

Interrupt mask register (Motor driver Ch. 1)

FFD8H

0

0

PTSEL1 PTSEL0

R

R/W

0

∗

3

0

∗

3

PTSEL1

PTSEL0

–

∗

2

–

∗

2

0

0

PWM

PWM

Normal

Normal

Unused

Unused

Programmable timer 1 PWM output selection

Programmable timer 0 PWM output selection

FFE0H

0

0

ECTC1 ECTC0

R

R/W

0

∗

3

0

∗

3

ECTC1

ECTC0

–

∗

2

–

∗

2

0

0

Enable

Enable

Mask

Mask

Unused

Unused

Interrupt mask register (Programmable timer 1 compare match)

Interrupt mask register (Programmable timer 0 compare match)

CD17

CD16

CD15

CD14

0

0

0

0

MSB

Programmable timer 1 compare data (high-order 4 bits)

LSB

R/W

FFD5H

CD17

CD16

CD15

CD14

CD13

CD12

CD11

CD10

0

0

0

0

MSB

Programmable timer 1 compare data (low-order 4 bits)

LSB

R/W

FFD4H

CD13

CD12

CD11

CD10

FFE1H

0

0

EIPT1

EIPT0

R

R/W

0

∗

3

0

∗

3

EIPT1

EIPT0

–

∗

2

–

∗

2

0

0

Enable

Enable

Mask

Mask

Unused

Unused

Interrupt mask register (Programmable timer 1 underflow)

Interrupt mask register (Programmable timer 0 underflow)

FFE3H

0

0

0

EIK0

R

R/W

0

∗

3

0

∗

3

0

∗

3

EIK0

–

∗

2

–

∗

2

–

∗

2

0

Enable

Mask

Unused

Unused

Unused

Interrupt mask register (K00–K03)

FFF0H

0

0

ICTC1

ICTC0

R

R/W

0

∗

3

0

∗

3

ICTC1

ICTC0

–

∗

2

–

∗

2

0

0

(R)

Yes

(W)

Reset

(R)

No

(W)

Invalid

Unused

Unused

Interrupt factor flag (Programmable timer 1 compare match)

Interrupt factor flag (Programmable timer 0 compare match)

FFE2H

0

0

0

EISIF

R

R/W

0

∗

3

0

∗

3

0

∗

3

EISIF

–

∗

2

–

∗

2

–

∗

2

0

Enable

Mask

Unused

Unused

Unused

Interrupt mask register (Serial I/F)