S1C63656 TECHNICAL MANUAL

EPSON

129

CHAPTER 4: PERIPHERAL CIRCUITS AND OPERATION (SVD Circuit)

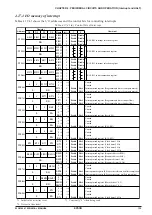

4.16.3 I/O memory of SVD circuit

Table 4.16.3.1 shows the I/O addresses and the control bits for the SVD circuit.

Table 4.16.3.1 Control bits of SVD circuit

Address

Comment

D3

D2

Register

D1

D0

Name

Init

∗

1

1

0

FF05H

0

0

SVDDT SVDON

R

R/W

0

∗

3

0

∗

3

SVDDT

SVDON

–

∗

2

–

∗

2

0

0

Low

On

Normal

Off

Unused

Unused

SVD evaluation data

SVD circuit On/Off

FF04H

0

SVDS2 SVDS1 SVDS0

R

R/W

0

∗

3

SVDS2

SVDS1

SVDS0

–

∗

2

0

0

0

Unused

SVD criteria voltage setting

(V1: when OSC3 is used, V2: when OSC3 is not used)

1

2.00

1.13

2

2.15

1.22

3

2.30

1.30

4

2.45

1.39

5

2.60

1.47

6

2.75

1.56

7

2.90

1.64

[SVDS2–0]

V1 (V)

V2 (V)

0

1.85

–

*1 Initial value at initial reset

*2 Not set in the circuit

*3 Constantly "0" when being read

SVDS2–SVDS0: SVD criteria voltage setting register (FF04H•D2–D0)

Criteria voltage for SVD is set as shown in Table 4.16.2.1.

At initial reset, this register is set to "0".

SVDON: SVD control (on/off) register (FF05H•D0)

Turns the SVD circuit on and off.

When "1" is written: SVD circuit ON

When "0" is written: SVD circuit OFF

Reading: Valid

When SVDON is set to "1", a source voltage detection is executed by the SVD circuit. As soon as SVDON

is reset to "0", the result is loaded to the SVDDT latch. To obtain a stable detection result, the SVD circuit

must be on for at least 500 µsec.

At initial reset, this register is set to "0".

SVDDT: SVD data (FF05H•D1)

This is the result of supply voltage detection.

When "0" is read: Supply voltage (V

DD

–V

SS

)

≥

Criteria voltage

When "1" is read: Supply voltage (V

DD

–V

SS

) < Criteria voltage

Writing: Invalid

The result of supply voltage detection at time of SVDON is set to "0" can be read from this latch.

At initial reset, SVDDT is set to "0".