132

EPSON

S1C63656 TECHNICAL MANUAL

CHAPTER 4: PERIPHERAL CIRCUITS AND OPERATION (Interrupt and HALT)

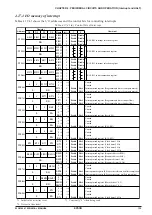

Fig. 4.17.1 Configuration of the interrupt circuit

Interrupt

vector

generation

circuit

Program

counter

(low-order 4 bits)

INT

Interrupt request

Interrupt factor flag

Interrupt mask register

Input comparison register

Interrupt selection register

Interrupt flag

NMI request

Watchdog timer

K10

KCP10

SIK10

K11

KCP11

SIK11

K12

KCP12

SIK12

K13

KCP13

SIK13

IK1

EIK1

IT3

EIT3

IT2

EIT2

IT1

EIT1

IT0

EIT0

IRUN

EIRUN

ILAP

EILAP

ISW1

EISW1

ISW10

EISW10

IRFM

EIRFM

IRFB

EIRFB

ISMD2

EISMD2

ISMD1

EISMD1

IPT1

EIPT1

IPT0

EIPT0

ICTC1

ECTC1

ICTC0

ECTC0

K00

KCP00

SIK00

K01

KCP01

SIK01

K02

KCP02

SIK02

K03

KCP03

SIK03

IK0

EIK0

ISIF

EISIF

IT4

EIT4