Rev. 1.43

User's

Guide

43

4

Software description

4.1. Introduction

The PowerQUICC II includes a very versatile and powerful memory controller.

This controller permits to define by software the base memory for each chip select, thus to define the

memory map.

The memory controller is composed of three internal machines:

-

The general purpose chip select machine: GPCM provides signal generation for

local resources: SRAM and FLASH memory, and Real Time Clock.

-

The synchronous DRAM machine provide signal generation for SDRAM devices.

This

internal

machine

supports

many special features for SDRAM.

-

The user programmable machines: UPM can be programmed by the user through

an internal array to provide specific patterns on signals. These UPMs are used to

control the IP and VME devices.

The error generation is mainly handled with the internal bus monitor included in the 8260. See the

SYPCR register and bus monitor description in the 8260 User's manual.

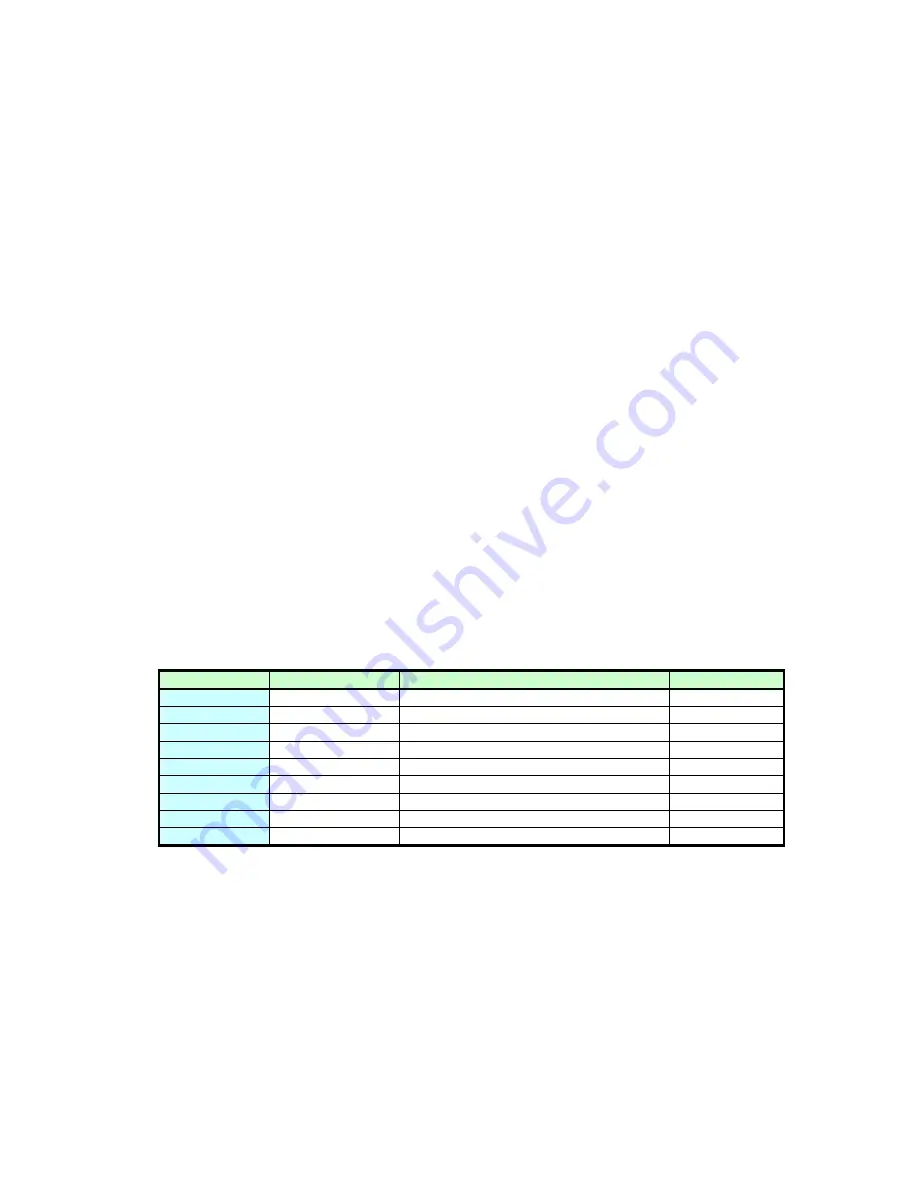

Here follows the description of all used chip select on the VSBC-6862:

Chip Select

Port size (bits)

Device

Size

CS0

32

Flash bank 0: boot device 0

8 MBytes

CS1

64 SDRAM

128

MBytes

CS2

32

Flash Bank 1: boot device 1

8 MBytes

CS3

8

Real Time Clock and SRAM

32 kBytes

CS4

16

IP ID, I/O + Board registers

32 kBytes

CS5

16

IP Mem

32 MBytes

CS6

8, 16, 32

VME window A

64 MBytes

CS7

8, 16, 32

VME window B

64 MBytes

CS9

32 SRAM

1

MBytes

In addition, the PowerQUICC II provides many internal peripherals as Fast Ethernet controllers, serial

controllers, etc...

These peripherals are internally handled by the MPC-8260 and the control signals are directly

connected to the external transceivers.

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com