MC97F6108A User’s manual

16. Inter Integrated Circuit (I2C)

169

16.2

I2C bit transfer

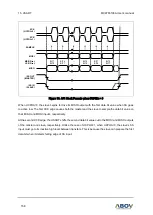

Data on the SDA line must be stable during HIGH period of the clock, SCL. The HIGH or LOW state of

the data line can only change when the clock signal on the SCL line is LOW. The exceptions are

START(S), repeated START(Sr) and STOP(P) condition where data line changes when clock line is

high.

Figure 76. Bit Transfer on the I2C-Bus

16.3

Start/ Repeated Start/ Stop

One master can issue a START (S) condition to notice other devices connected to the SCL, SDA lines

that it will use the bus. A STOP (P) condition is generated by the master to release the bus lines so that

other devices can use it.

A high to low transition on the SDA line while SCL is high defines a START (S) condition.

A low to high transition on the SDA line while SCL is high defines a STOP (P) condition.

START and STOP conditions are always generated by the master. The bus is considered to be busy

after START condition. The bus is considered to be free again after STOP condition, i.e., the bus is

busy between START and STOP condition. If a repeated START condition (Sr) is generated instead of

STOP condition, the bus stays busy. So, the START and repeated START conditions are functionally

identical.

Figure 77. START and STOP Condition

SCL

SDA

Data line Stable:

Data valid

except S, Sr, P

Change of Data

allowed

SCL

SDA

START Condition

S

P

STOP Condition