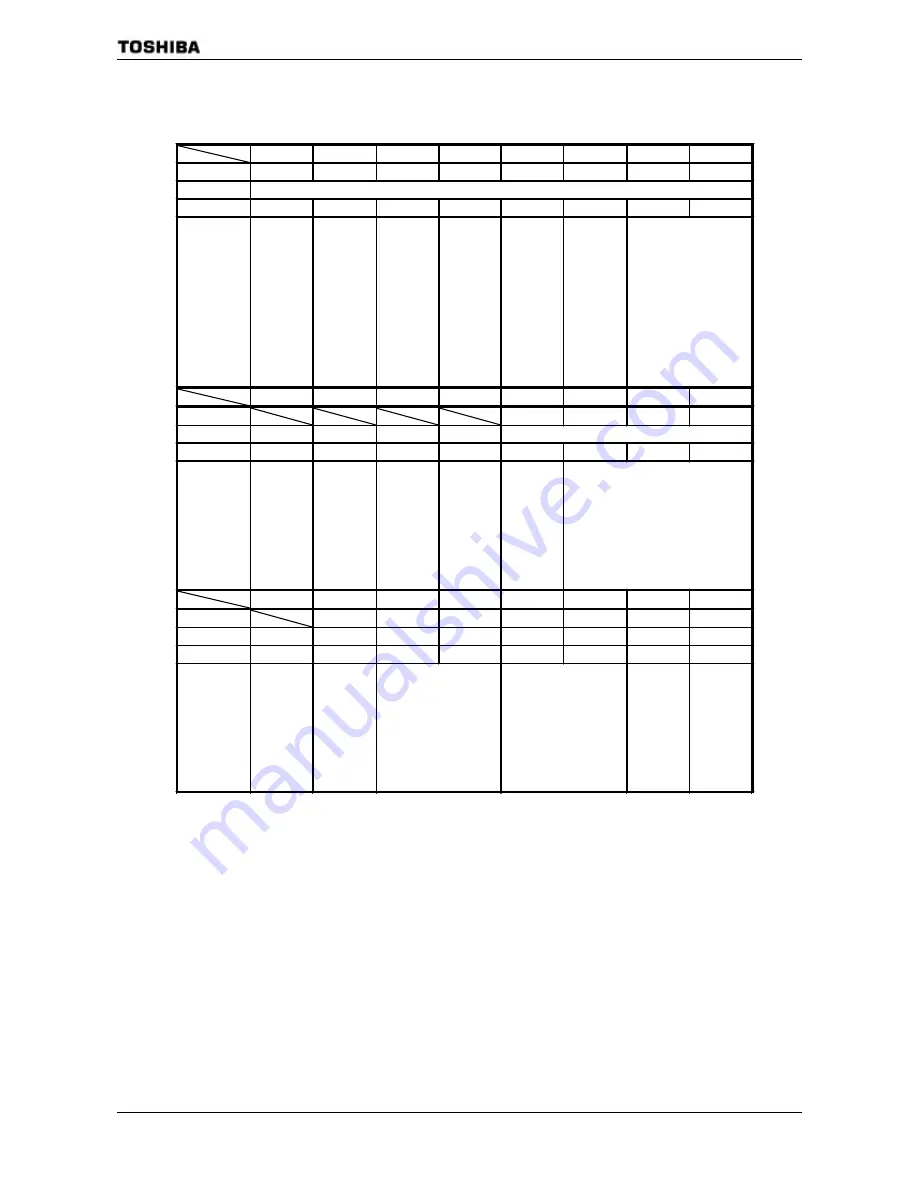

TMP91C824

91C824-15

3.3.2

SFR

7

6

5

4

3

2

1

0

bit Symbol

XEN

XTEN

RXEN

RXTEN

RSYSCK

WUEF

PRCK1

PRCK0

Read/Write

R/W

After reset

1

1

1

0

0

0

0

0

Function

High -frequen

cy oscillator

(fc)

0: Stop

1: Oscillation

Low-frequen

cy oscillator

(fs)

0: Stop

1: Oscillation

(note1)

High-frequen

cy oscillator

(fc) after

release of

Stop Mode

0: Stop

1: Oscillation

Low-frequen

cy oscillator

(fs) after

release of

Stop Mode

0: Stop

1: Oscillation

Selects clock

after release

of Stop

Mode

0: fc

1: fs

Warm-up

Timer

0: Write

Don’t care

1: Write

start timer

0: Read

end warm-up

1: Read

do not end

warm-up

Select prescaler clock

00: fFPH (note2)

01: reserved

10: fc/16

11: reserved

7

6

5

4

3

2

1

0

bit Symbol

SYSCK

GEAR2

GEAR1

GEAR0

Read/Write

R/W

After reset

0

1

0

0

Function

Select

system clock

0: fc

1: fs

Select gear value of high frequency (fc)

000: fc

001: fc/2

010: fc/4

011: fc/8

100: fc/16

101: ( reserved)

110: ( reserved)

111: ( reserved)

7

6

5

4

3

2

1

0

bit Symbol

SCOSEL

WUPTM1

WUPTM0

HALTM1

HALTM0

SELDRV

DRVE

Read/Write

R/W

R/W

R/W

R/W

R/W

R/W

R/W

After reset

0

1

0

1

1

0

0

Function

0: fs

1: f

SYS

Warm-Up Timer

00: reserved

01: 2

8

/inputted frequency

10:2

1 4

11:2

1 6

HALT mode

00: reserved

01: STOP mode

10: IDLE1 mode

11: IDLE2 mode

<DRVE>

mode

select

0: STOP

1: IDLE1

Pin state

control in

STOP/IDLE1

mode

0: I/O off

1: Remains

the state

before

HALT

SYSCR0

(00E0H)

SYSCR1

(00E1H)

SYSCR2

(00E2H)

(note1) By Reset, low-frequency oscillator is enable.

(note2) In case of using built-in SBI circuit, it must set SYSCR0<PRCK1:0> to ‘00’.

Figure 3.3.3 SFR for system clock