xE922-3GR Hardware User Guide

1VV0301272

Rev.0.8 2017-01-05

Reproduction forbidden without written authorization from Telit Communications S.p.A. - All Rights

Reserved.

Page 75 of 112

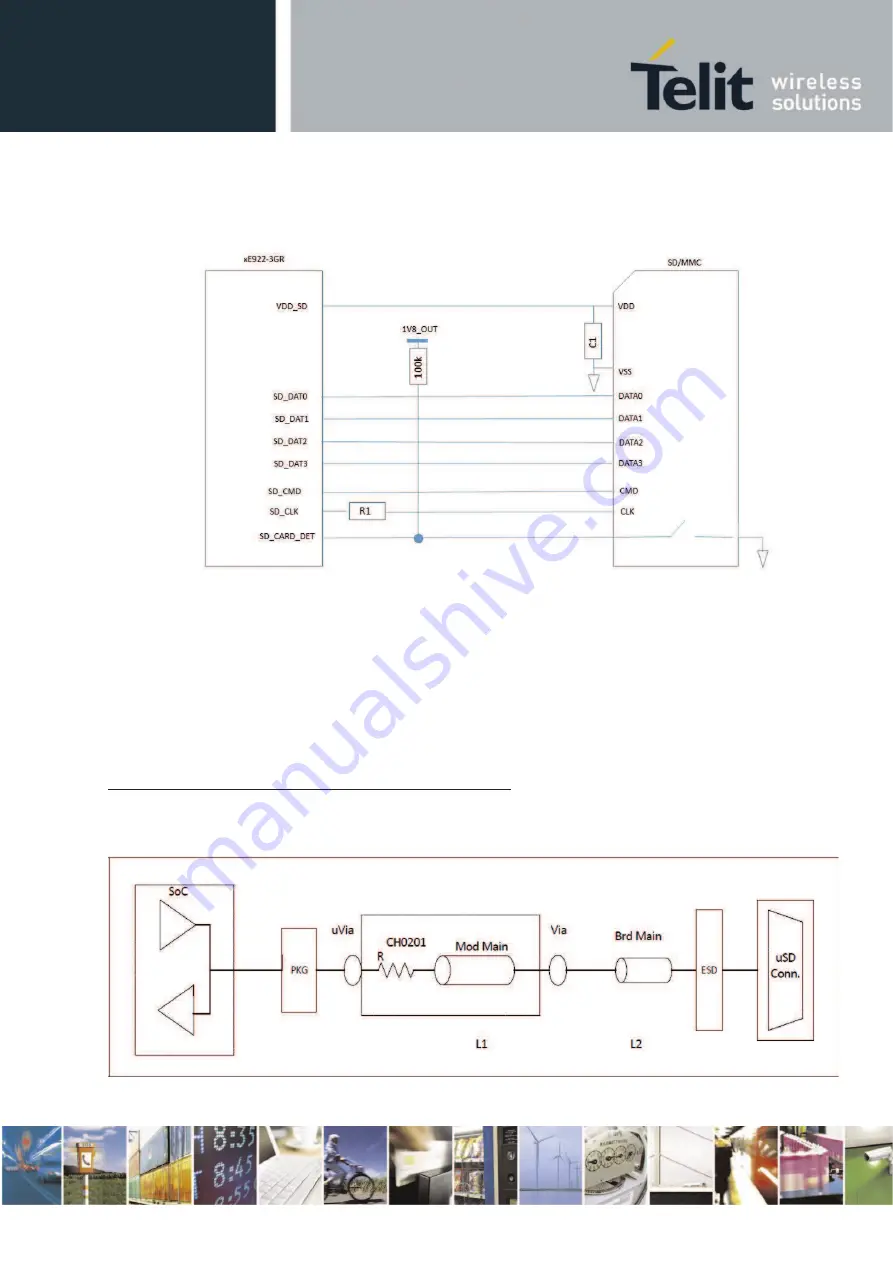

A typical diagram for SDMMC card connection is shown in below figure.

Series resistor R1 place holder is recommended for tuning high speed CLK signal, typ.27 Ohm.

Internal regulator VDD_SD supports dual voltage level 2.9V (default)/1.8V, with current rating max 255 mA.

Maximum decoupling capacitance C1 is up to 5 uF (including the internal 1uF decoupling already present).

In case ESD protection to be applied, use high speed device < 2pF.

Routing guide lines for the display SDMMC/SDIO interface:

The next figure shows a typical signal traject with different sub trajects.