Hardware layout and configuration

UM1668

18/70

DocID025151 Rev 2

2.13 Ethernet

The STM32439I-EVAL evaluation board supports 10M/100M Ethernet communication by a

PHY DP83848CVV (U5) and integrated RJ45 connector (CN10). Ethernet PHY is

connected to the STM32F439NIH6 via the MII interface.

A 25 MHz clock can be generated by PHY or provided by MCO from the STM32F439NIH6

by setting jumper JP6 as shown in

Table 10

.

Note:

Ethernet works properly in the default setting (which RX_ER is not connected to PI10 of

STM32F439NIH6) because PI10 is shared with data signal of SDRAM. If RX_ER signal is

needed, remove R244 and solder R43.

2.14 Extension

connector

An extension connector (CN2) is intended for external board connection to the STM32439I-

EVAL evaluation board using cable FFSD-05-D-04.00-01-N.

The external board can exchange data with the STM32F439NIH6 via the I2C1 or SPI3

ports.

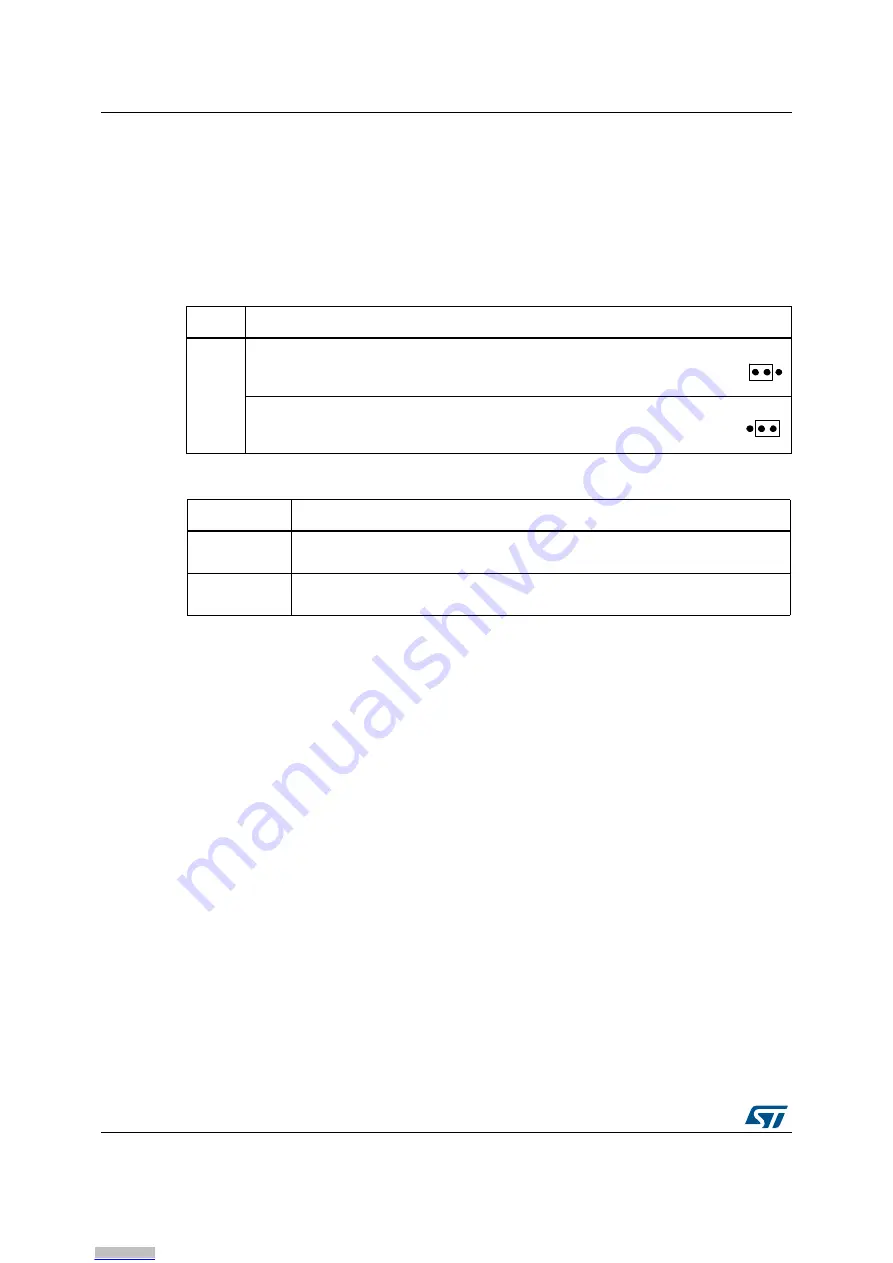

Table 10. Ethernet related jumper

Jumper Description

JP6

25 MHz clock is provided by external Crystal X4 when JP5 is set as shown to

the right: (Default setting)

25 MHz clock for MII is provided by MCO at PA8 when JP5 is set as shown to

the right:

Table 11. Ethernet related solder bridges

Solder bridges Description

SB7

MII CRS on DP83848CVV is connected to PA0 when SB7 is closed. PA0 is shared

with Wakeup button and MC_ENA. Default setting: Open

SB8

MII COL on DP83848CVV is connected to PH3 when SB8 is closed. PH3 is shared

with SDRAM chip select SDNE0. Default setting: Open

1 2 3

1 2 3

Downloaded from

Downloaded from

Downloaded from

Downloaded from

Downloaded from

Downloaded from

Downloaded from

Downloaded from

Downloaded from

Downloaded from

Downloaded from

Downloaded from

Downloaded from

Downloaded from

Downloaded from

Downloaded from

Downloaded from

Downloaded from