RTD Embedded Technologies, Inc.

| www.rtd.com

v

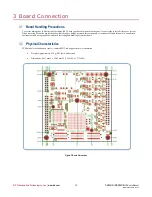

DM35418HR/DM35218HR

User’s Manual

BDM-610010041 Rev F

Initializing the ADC Converter

Simplified block diagram of analog input

5.4.3.1. Single Ended, Bipolar, ±10V Full-scale range

5.4.3.2. Differential, Bipolar, ±10V Full-scale range

5.4.3.3. Single Ended, Unipolar, 0-10V Full-scale range

5.4.3.4. Differential, Unipolar, 0-10V Full-scale range

5.4.3.5. ADC Gain and Offset Test

Initializing the DAC Converter

Simplified block diagram of analog output

FB_DMAm_Last_Action (Read/Write)

FB_DMAm_Stat_Used (Read/Write)

FB_DMAm_Stat_Invalid (Read/Write)

FB_DMAm_Stat_Overflow (Read/Write)

FB_DMAm_Stat_Underflow (Read/Write)

FB_DMAm_Stat_Complete (Read/Write)

FB_DMAm_Current_Buffer (Read-Only)

FB_DMAm_RD_FIFO_CNT(Read-Only)

FB_DMAm_WR_FIFO_CNT(Read-Only)