RTD Embedded Technologies, Inc.

| www.rtd.com

40

DM35418HR/DM35218HR

User’s Manual

BDM-610010041 Rev F

6.4

BAR2: Analog to Digital Converter (ADC)

This Function Block is for an Analog to Digital converter. The DM35418 has eight ADC Function blocks, one for each of the eight ADC inputs.

The ADC0 input is associated with the lowest-numbered ADC Function Block, and ADC7 is associated with the highest-numbered ADC

Function Block. Each Function Block has its own clock, triggers, and DMA channel.

This Function Block is for an Analog to Digital converter. The DM35218 has four ADC Function blocks, one for each of the four ADC inputs.

The ADC0 input is associated with the lowest-numbered ADC Function Block, and ADC3 is associated with the highest-numbered ADC

Function Block. Each Function Block has its own clock, triggers, and DMA channel.

6.4.1

F

UNCTION

B

LOCK

R

EGISTER

M

AP

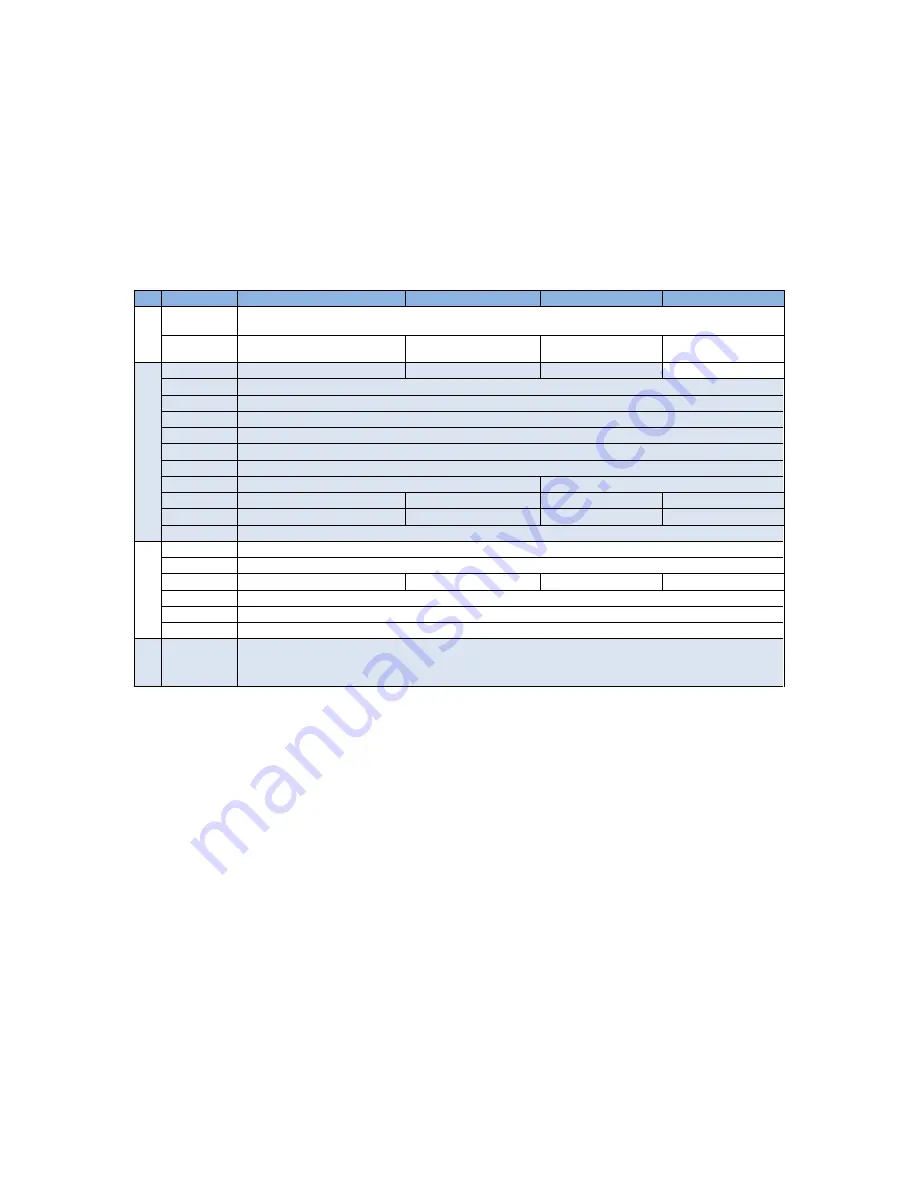

Table 22: Multi-Channel A/D Functional Block

Offset

0x03

0x02

0x01

0x00

H

ea

de

r FB + 0x00

FB_ID

FB + 0x04

FB_DMA_BUFFERS

FB_DMA_CHANNELS

Reserved

Reserved

AD

C

C

ont

rol

FB + 0x08

STOP_TRIG

START_TRIG

CLK_SRC

MODE_STATUS

FB + 0x0C

CLK_DIV

FB + 0x10

CLK_DIV_CNTR

FB + 0x14

PRE_TRIGGER_CAPTURE (limited by FIFO size)

FB + 0x18

POST_STOP_CAPTURE

FB + 0x1C

SAMPLE_CNT

FB + 0x20

INT_ENA (Sample, Start, Stop, Threshold, Pacer Tick, etc)

FB + 0x24

INT_STAT

Reserved

FB + 0x28

CLK_SRC_GBL3

CLK_SRC_GBL2

Reserved

FB + 0x2C

CLK_SRC_GBL7

CLK_SRC_GBL6

CLK_SRC_GBL5

CLK_SRC_GBL4

FB + 0x30

AD_CONFIG (Maskable register – 16-bit)

AD

C

C

han

ne

l FB + 0x34

CH_FRONT_END_CONFIG (Maskable register – 16-bit)

FB + 0x38

CH_FIFO_DATA_CNT

FB + 0x3C

CH_INT_ENA

CH_INT_STAT

CH_FILTER

Reserved

FB + 0x40

CH_THRESH_LOW

FB + 0x44

CH_THRESH_HIGH

FB + 0x48

CH_LAST_SAMPLE

FIF

O

FB + 0x4C

CH_FIFO_ACCESS

6.4.2

M

ODE

_S

TATUS

(R

EAD

/W

RITE

,

R

EAD

-O

NLY

)

Selects the current mode of operation and indicates its triggering status.

B[3:0]: Mode

o

0x04: Uninitialized. This is the power-on state. No converter initialization has taken place. Sampling is stopped, and all

counters are reset and the triggering state machine is reset. Transition to any of the other Modes will start converter

initialization (sampling will not start until initialization is complete).

o

0x00: Reset. Sampling is stopped. All counters are reset and the triggering state machine is reset.

o

0x01: Paused. Sampling is stopped, but the counters and triggering state machine maintain their state.

o

0x02: Go, Single-Shot. After filling the buffer with the Post-Stop samples, capturing stops. The Mode must be set back to

RESET in order to capture more samples.

o

0x03: Go, Re-arm. After filling the buffer with the Post-Stop samples and the FIFO is empty, the triggering state machine

is restarted, i.e. FIFO is filled with Pre-Start samples and waits for a start trigger.