RTD Embedded Technologies, Inc.

| www.rtd.com

39

DM35418HR/DM35218HR

User’s Manual

BDM-610010041 Rev F

6.2.15

FB_DMA

M

_CTRL

N

(R

EAD

/W

RITE

)

B0: Valid: Driver sets to ‘1’ to indicate that this contains valid information. The DMA engine will set the error bit and halt if it is

ready to use this descriptor and it is not valid.

B1: Halt: Driver sets to ‘1’ to halt the DMA engine after this buffer is full.

B2: Loop: Driver sets to ‘1’ to start back at descriptor 0 after this buffer is full. This has a higher priority than the HALT bit.

B3: Interrupt: Driver sets to ‘1’ to generate an interrupt after this buffer is full.

B4: Pause: Driver sets to ‘1’ to pause the DMA engine after this buffer is full.

If the last buffer is reached, and the HALT and LOOP bits are both ‘0’, the DMA engine will loop.

If the last buffer is reached, and the HALT and LOOP bits are both ‘1’, the DMA engine will halt and the Current_Buffer will be set to 0.

6.2.16

FB_DMA

M

_STAT

N

(R

EAD

/C

LEAR

)

B0: Used (R/C): DMA engine sets to ‘1’ to indicate that it has completely used this descriptor. The driver must clear this bit when it

is ready to be used again. The DMA engine will set the error bit and PAUSE if it is ready to use this descriptor and the Used bit is

set, unless the

bit is set. The bits are cleared by writing 0x00 to the byte.

6.3

BAR2: Functional Block Header Registers

Each Functional Block has a standard header as follows.

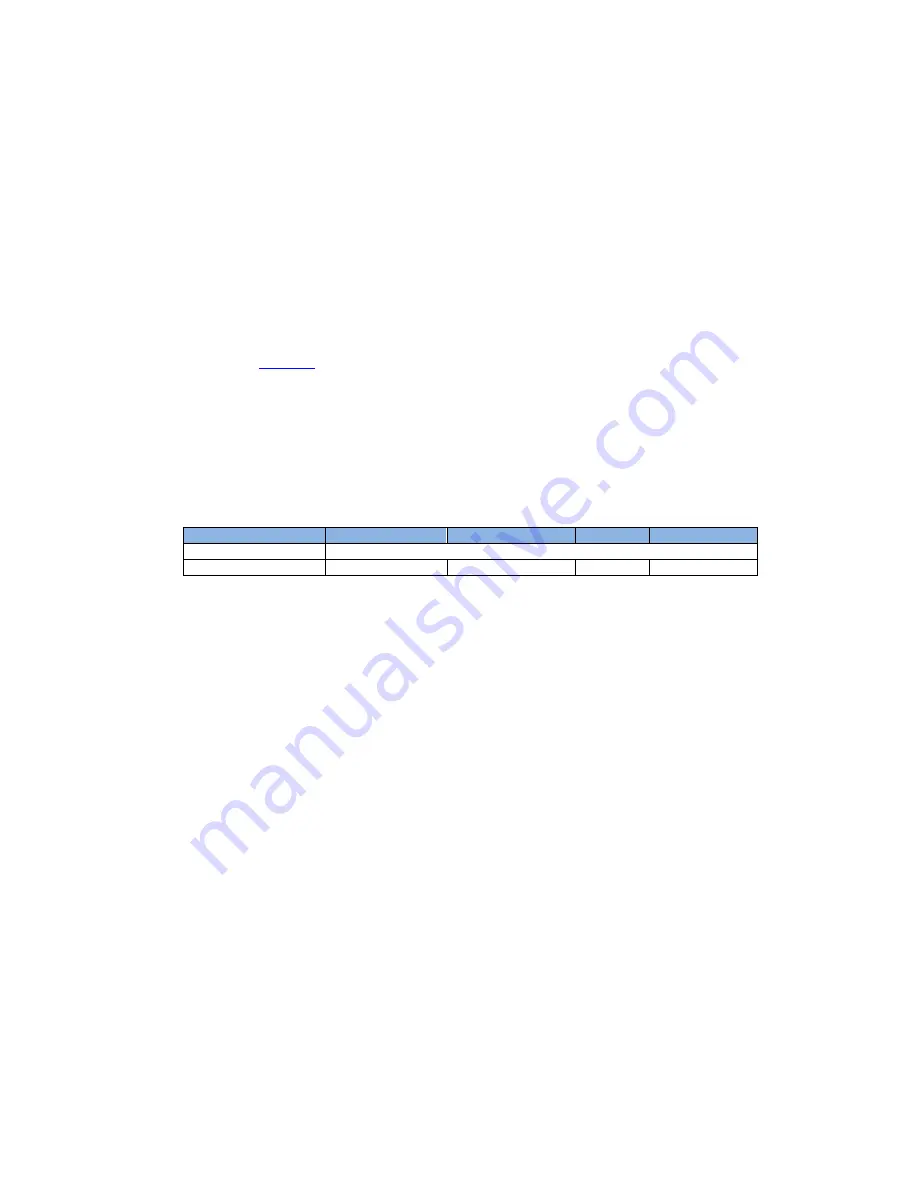

Table 21: Functional Block Header

Offset

0x03

0x02

0x01

0x00

FB + 0x00

FB_ID

FB + 0x04

FB_DMA_BUFFERS

FB_DMA_CHANNELS Reserved

Reserved

6.3.1

FB_ID

(R

EAD

-O

NLY

)

This is a repeat of the ID from the General Board Control section. This can be used to validate that the correct Function Block is being accessed.

6.3.2

FB_DMA_CHANNELS

(R

EAD

-O

NLY

)

This register contains the number of DMA Channels in this Function Block.

6.3.3

FB_DMA_BUFFERS

(R

EAD

-O

NLY

)

This register contains the number of Buffer Descriptors in each DMA Channel.