R01UH0823EJ0100 Rev.1.00

Page 1445 of 1823

Jul 31, 2019

RX23W Group

40. SD Host Interface (SDHIa)

40.2.20 SDHI Software Reset Register (SDRST)

lists the bits and flags initialized by the SDHI software reset.

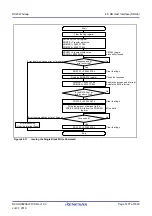

SDRST

Address(es): SDHI.SDRST 0008 ADC0h

b31

b30

b29

b28

b27

b26

b25

b24

b23

b22

b21

b20

b19

b18

b17

b16

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

Value after reset:

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

b15

b14

b13

b12

b11

b10

b9

b8

b7

b6

b5

b4

b3

b2

b1

b0

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

SDRST

Value after reset:

0

0

0

0

0

0

0

0

0

0

0

0

0

1

1

1

Bit

Symbol

Bit Name

Description

R/W

b0

SDHI Software Reset Control

0: SDHI software reset

1: SDHI software reset released

R/W

b2, b1

—

Reserved

These bits are 1 when read. Set them to 1 when writing.

R

b31 to b3

—

Reserved

These bits are 0 when read and cannot be modified.

R

Table 40.5

Bits and Flags Initialized by the SDHI Software Reset

Register

Bit/Flag

CMDE, CRCE, ENDE, DTO, ILW, ILR, RSPTO, SDD0MON, BRE, BWE, SDCLKCREN, ILA

CTOP[3:0], TOP[3:0], WIDTH

Bits b8 and b13 in the SDOPT register are also initialized by the SDHI software reset.

CMDE0, CMDE1, RSPLENE0, RSPLENE1, RDLENE, CRCLENE, RSPCRCE0, RSPCRCE1, RDCRCE, CRCTKE,

CRCTK[2:0]