R01UH0092EJ0110 Rev.1.10

Page 344 of 807

Jul 31, 2012

M16C/64C Group

19. Three-Phase Motor Control Timer Function

19.3.1.2

Three-Phase PWM Wave Control

Timer A4 controls U- and

U

-phase waveforms, timer A1 controls V- and

V

-phase waveforms, and

timer A2 controls W- and

W

-phase waveforms. Timer Ai (i = 1, 2, 4) starts counting by a trigger

selected by the INV10 bit in the INVC1 register, and generates a one-shot pulse (internal signal). The

output signal of each phase changes at the falling edge of the one-shot pulse.

Triangular wave modulation three-phase mode 1 counts values in the TAi1 register and TAi register

alternately, and generates a one-shot pulse.

19.3.1.3

Dead Time Control

Due to delays in the transistors turning off, the upper and lower transistors are turned on

simultaneously. To prevent this, there are three 8-bit dead time timers, one in each phase. The reload

resistor is shared. When the INV15 bit in the INVC1 register is 0 (dead time enabled), the dead time

set in the DTT register is enabled. When the INV15 bit is 1 (dead time disabled), no dead time is set.

Select a count source for the dead time timer by setting the INV12 bit in the INVC1 register.

A trigger for the dead time timer can be selected by setting the INV16 bit in the INVC1 register.

When both of the following conditions are met, set the INV16 bit to 1 (the rising edge of the three-

phase output shift register is a trigger for the dead time timer):

•

The INV15 bit is 0 (dead time enabled).

•

Bits Dij and DiBj in the IDBj register have different values when the INV03 bit in the INVC0 register

is 1 (three-phase motor control timer output enabled) (i = U, V or W; j = 0, 1). (During the period

other than dead time, the high- and low-side output signals always output opposite level signals.)

If either of the conditions above is not met, set the INV16 bit to 0 (a trigger for the dead time timer is

the falling edge of one-shot pulse of the timer).

In sawtooth wave modulation mode, the generation of a transfer trigger causes a trigger for the dead

time timer.

19.3.1.4

Output Level of Three-Phase PWM Output Pins

Set values to registers IDB0 and IDB1 to select the state of each high- or low-side output signal

(either active (on) or not active (off)). The values of registers IDB0 and IDB1 are transferred to the

three-phase output shift registers by a transfer trigger. After a transfer trigger is generated, the value

set in the IDB0 register becomes the first output signal of each phase (internal signal), and then at

the falling edge of a timer A1, A2, or A4 (internal signal) one-shot pulse, the value set in the IDB1

register becomes the output signal of each phase.

A transfer trigger is generated under any of the following conditions:

•

At the first timer B2 underflow after registers IDB0 and IDB1 are written (in triangular wave

modulation mode)

•

Each time timer B2 underflows (in sawtooth wave modulation mode)

•

Writing to the TB2 register while timer B2 is stopped (when the INV10 bit in the INVC1 register is 1)

•

Setting the INV07 bit in the INVC0 register to 1 (software trigger)

The active level can be selected by the INV14 bit in the INVC1 register.

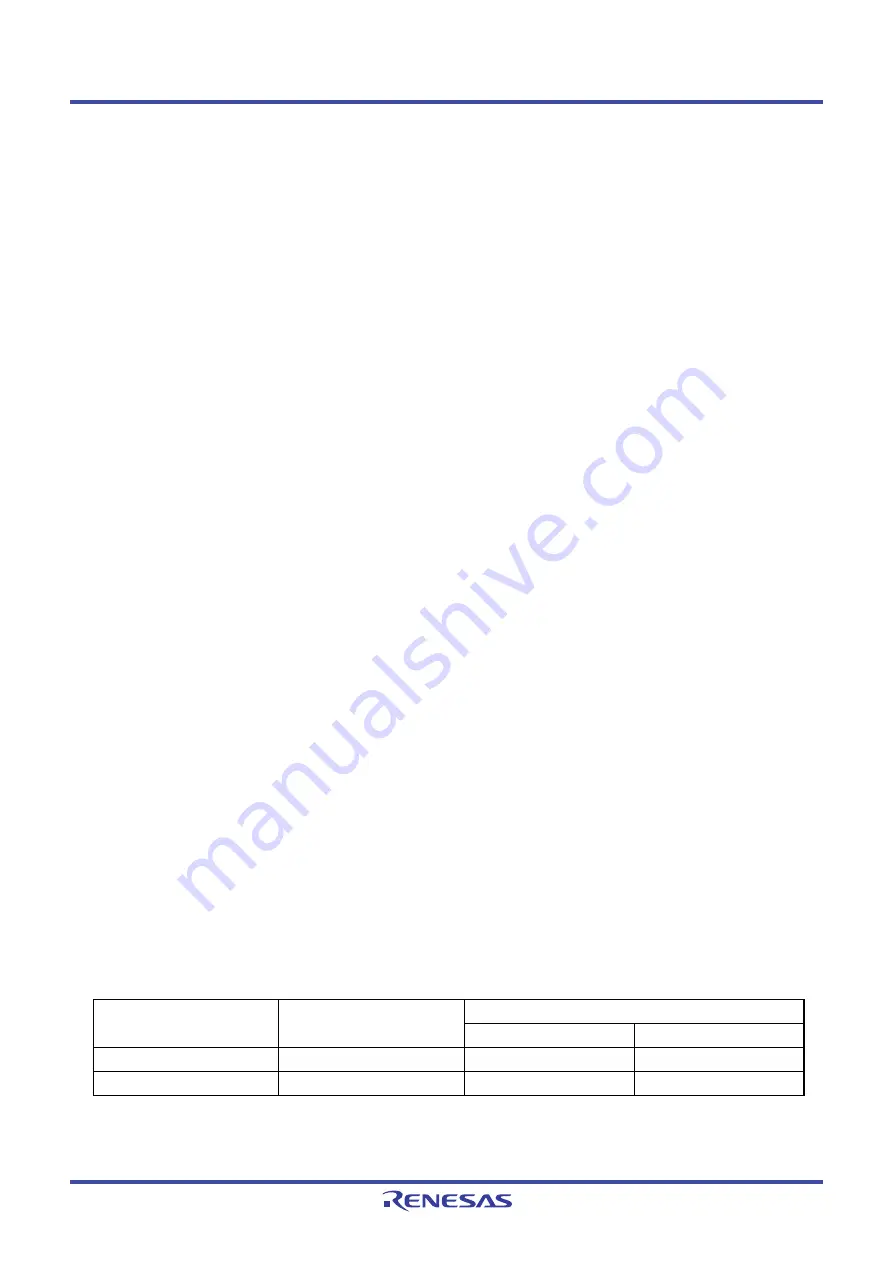

Table 19.7

Output Level of Three-Phase PWM Output Pins

Value Set in Registers

IDB0 and IDB1

Output Signal of Each

Phase (Internal Signal)

Value Set to the INV14 Bit in the INVC1 Register

0 (active, low level)

1 (active, high level)

0 (active (on))

0

Low

High

1 (not active (off))

1

High

Low

Содержание M16C Series

Страница 846: ...M16C 64C Group R01UH0092EJ0110...