CHAPTER 4 CAUTIONS

31

4.6

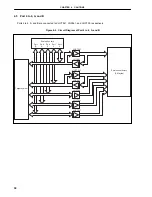

Bus Interface Pin

There are the following differences between the emulator and the target device in the operation of the pins for bus

interface.

Table 4-2. Bus Interface Pin Operation List (1/3)

(a) During break

Internal Memory

External Memory

Internal

ROM

Internal RAM

Internal

Peripheral I/O

Emulation RAM

Target System

Pin Name

Waiting for Emulator

Command

R

R

W

R

W

R

W

R

W

A0 to A23

Note

Note

Note

Note

D0 to D15

Hi-Z

Hi-Z

Note

Note

WE

H

H

H

Note

OE

H

H

H

Note

RD

H

H

H

Note

ADV/BCYST

Note

H

Note

Note

UWR/UCAS

H

H

H

Note

LWR/LCAS

H

H

H

Note

IORD

H

H

H

Note

IOWR

H

H

H

Note

CS0 to CS7

H

H

H

Note

RAS0 to RAS7

H

H

H

Note

REFRQ

H

H

H

Note

WAIT

Invalid

Note

Maskable

HLDRQ

Maskable

Maskable

Maskable

HLDAK

Note

Note

Note

Note

Performs the same operation as the cycle that is generated by the target device program execution.

Remarks 1.

R

: Read

W

: Write

2.

H

: High-level output

Hi-Z : High-impedance

Содержание IE-703102-MC-EM1

Страница 2: ...2 MEMO ...

Страница 10: ...10 MEMO ...

Страница 24: ...24 MEMO ...

Страница 26: ...26 MEMO ...

Страница 34: ...34 MEMO ...

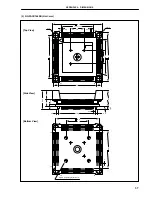

Страница 36: ...APPENDIX A DIMENSIONS 36 2 SC 144SD Unit mm 109 144 72 37 108 1 73 36 43 13 13 40 130 43 213 46 ...

Страница 40: ...40 MEMO ...

Страница 46: ...46 MEMO ...

Страница 48: ...48 MEMO ...