2-2

|

ni.com

Chapter 2

Analog Input

Analog Input Timing Signals

The cDAQ chassis features the following analog input timing signals:

•

•

AI Sample Clock Timebase Signal

•

*

•

•

Signals with an * support digital filtering. Refer to the

, for more information.

AI Convert Clock Signal Behavior For Analog Input Modules

section for AI Convert

Clock signals and the cDAQ chassis.

AI Sample Clock Signal

A sample consists of one reading from each channel in the AI task. Sample Clock signals the

start of a sample of all analog input channels in the task. Sample Clock can be generated from

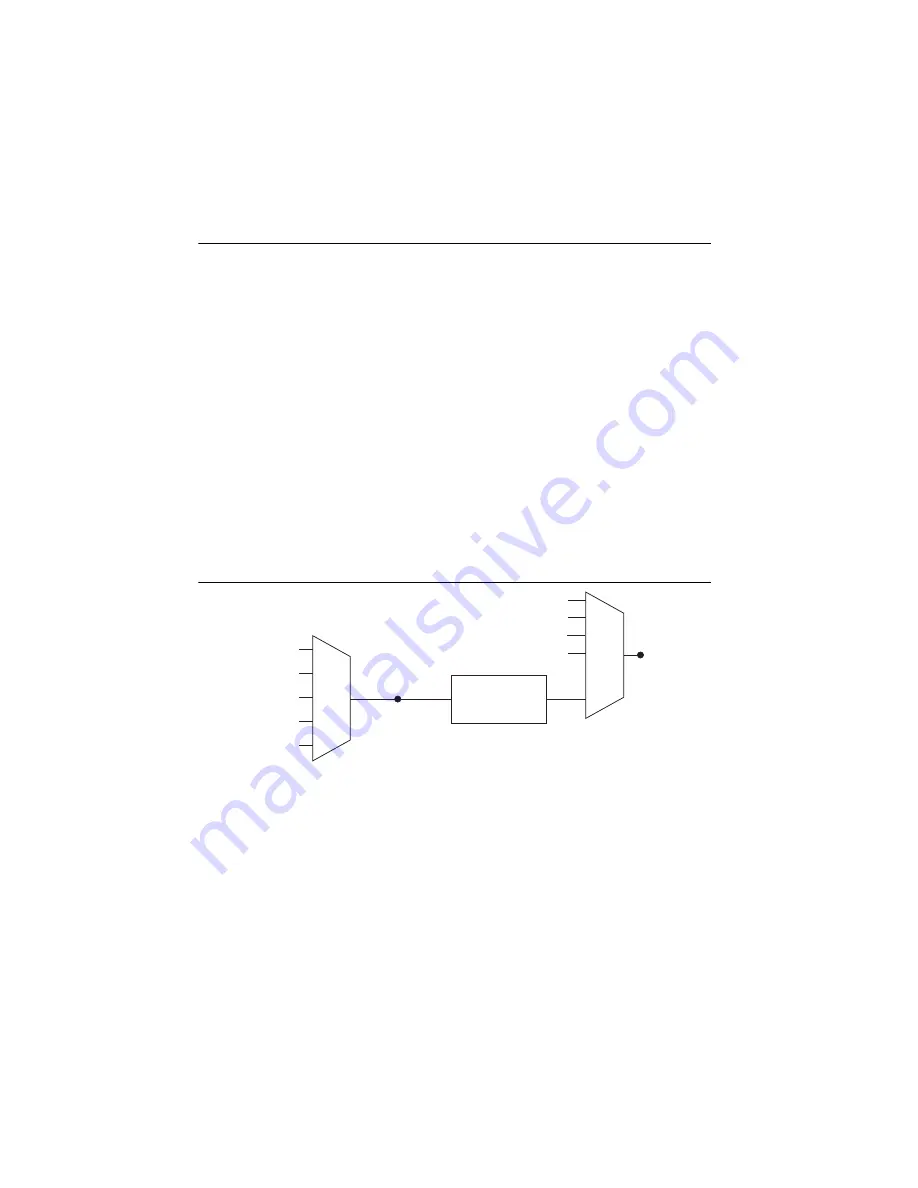

external or internal sources as shown in Figure 2-1.

Figure 2-1.

AI Sample Clock Timing Options

Routing the Sample Clock to an Output Terminal

You can route Sample Clock to any output PFI terminal. Sample Clock is an active high pulse

by default.

AI Sample Clock Timebase Signal

The AI Sample Clock Timebase signal is divided down to provide a source for Sample Clock.

AI Sample Clock Timebase can be generated from external or internal sources. AI Sample Clock

Timebase is not available as an output from the chassis.

Progr

a

mm

ab

le

Clock

Divider

AI

Sa

mple Clock

Time

bas

e

PFI

An

a

log Comp

a

ri

s

on Event

Ctr

n

Intern

a

l O

u

tp

u

t

AI

Sa

mple Clock

S

igm

a

-Delt

a

Mod

u

le Intern

a

l O

u

tp

u

t

An

a

log Comp

a

ri

s

on

Event

20 MHz Time

bas

e

8

0 MHz Time

bas

e

PFI

100 kHz Time

bas

e