3.2 Program Execution State

In this state the CPU executes program instructions in normal sequence.

3.3 Exception-Handling State

The exception-handling state is a transient state that occurs when the CPU alters the normal

program flow due to a reset, interrupt, or trap instruction. The CPU fetches a starting address from

the exception vector table and branches to that address. In interrupt exception handling the CPU

references the stack pointer (ER7) and saves the program counter and condition-code register.

3.3.1 Types of Exception Handling and Their Priority

Exception handling is performed for resets, interrupts, and trap instructions. Table 3-1 indicates

the types of exception handling and their priority.

Table 3-1 Exception Handling Types and Priority

Priority

Type of Exception

Detection Timing

Start of Exception Handling

High

Reset

Synchronized with

Exception handling starts

clock

immediately when RES changes

from low to high

Interrupt

End of instruction

When an interrupt is requested,

execution (see note)

exception handling starts at the end

of the current instruction or current

exception-handling sequence

Trap instruction

When TRAPA

Exception handling starts when a

Low

instruction is executed

trap (TRAPA) instruction is executed

Note: Interrupts are not detected at the end of the ANDC, ORC, XORC, and LDC instructions, or

immediately after reset exception handling.

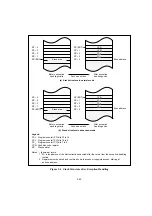

Figure 3-3 classifies the exception sources. For further details about exception sources, vector

numbers, and vector addresses refer to the relevant microcontroller hardware manual.

Figure 3-3 Classification of Exception Sources

Exception sources

Reset

Interrupt

Trap instruction

External interrupts

Internal interrupts (from on-chip supporting modules)

241