204

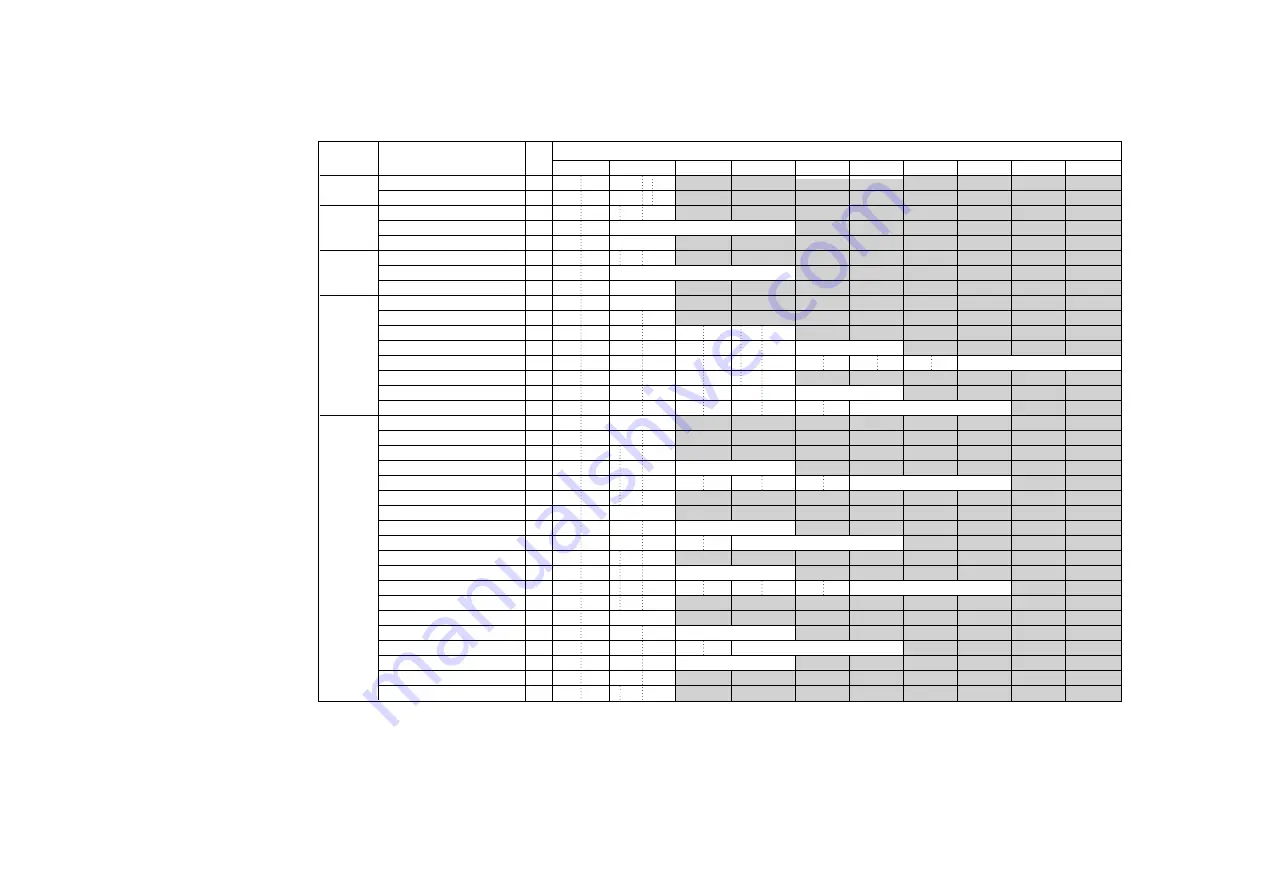

Table 2-3 Instruction Codes (cont)

Instruction Format

1st byte

2nd byte

3rd byte

4th byte

5th byte

6th byte

7th byte

8th byte

9th byte

10th byte

INC

INC.L #1,ERd

L

0

B

7

0 erd

INC.L #2,ERd

L

0

B

F

0 erd

JMP

JMP @ERn

—

5

9

0 ern

0

JMP @aa:24

—

5

A

abs

JMP @@aa:8

—

5

B

abs

JSR

JSR @ERn

—

5

D

0 ern

0

JSR @aa:24

—

5

E

abs

JSR @@aa:8

—

5

F

abs

LDC

LDC #xx:8,CCR

B

0

7

IMM

LDC Rs,CCR

B

0

3

0

rs

LDC @ERs,CCR

W

0

1

4

0

6

9

0 ers

0

LDC @(d:16,ERs),CCR

W

0

1

4

0

6

F

0 ers

0

disp

LDC @(d:24,ERs),CCR

W

0

1

4

0

7

8

0 ers

0

6

B

2

0

0 0

disp

LDC @ERs+,CCR

W

0

1

4

0

6

D

0 ers

0

LDC @aa:16,CCR

W

0

1

4

0

6

B

0

0

abs

LDC @aa:24,CCR

W

0

1

4

0

6

B

2

0

0

0

abs

MOV

MOV.B #xx:8,Rd

B

F

rd

IMM

MOV.B Rs,Rd

B

0

C

rs

rd

MOV.B @ERs,Rd

B

6

8

0 ers

rd

MOV.B @(d:16,ERs),Rd

B

6

E

0 ers

rd

disp

MOV.B @(d:24,ERs),Rd

B

7

8

0 ers

0

6

A

2

rd

0

0

disp

MOV.B @ERs+,Rd

B

6

C

0 ers

rd

MOV.B @aa:8,Rd

B

2

rd

abs

MOV.B @aa:16,Rd

B

6

A

0

rd

abs

MOV.B @aa:24,Rd

B

6

A

2

rd

0

0

abs

MOV.B Rs,@ERd

B

6

8

1 erd

rs

MOV.B Rs,@(d:16,ERd)

B

6

E

1 erd

rs

disp

MOV.B Rs,@(d:24,ERd)

B

7

8

0 erd

0

6

A

A

rs

0

0

disp

MOV.B Rs,@–ERd

B

6

C

1 erd

rs

MOV.B Rs,@aa:8

B

3

rs

abs

MOV.B Rs,@aa:16

B

6

A

8

rs

abs

MOV.B Rs,@aa:24

B

6

A

A

rs

0

0

abs

MOV.W #xx:16,Rd

W

7

9

0

rd

IMM

MOV.W Rs,Rd

W

0

D

rs

rd

MOV.W @ERs,Rd

W

6

9

0 ers

rd

Instruction

Mnemonic

Size