DIVXU

DIVXU (DIVide eXtend as Unsigned)

Divide

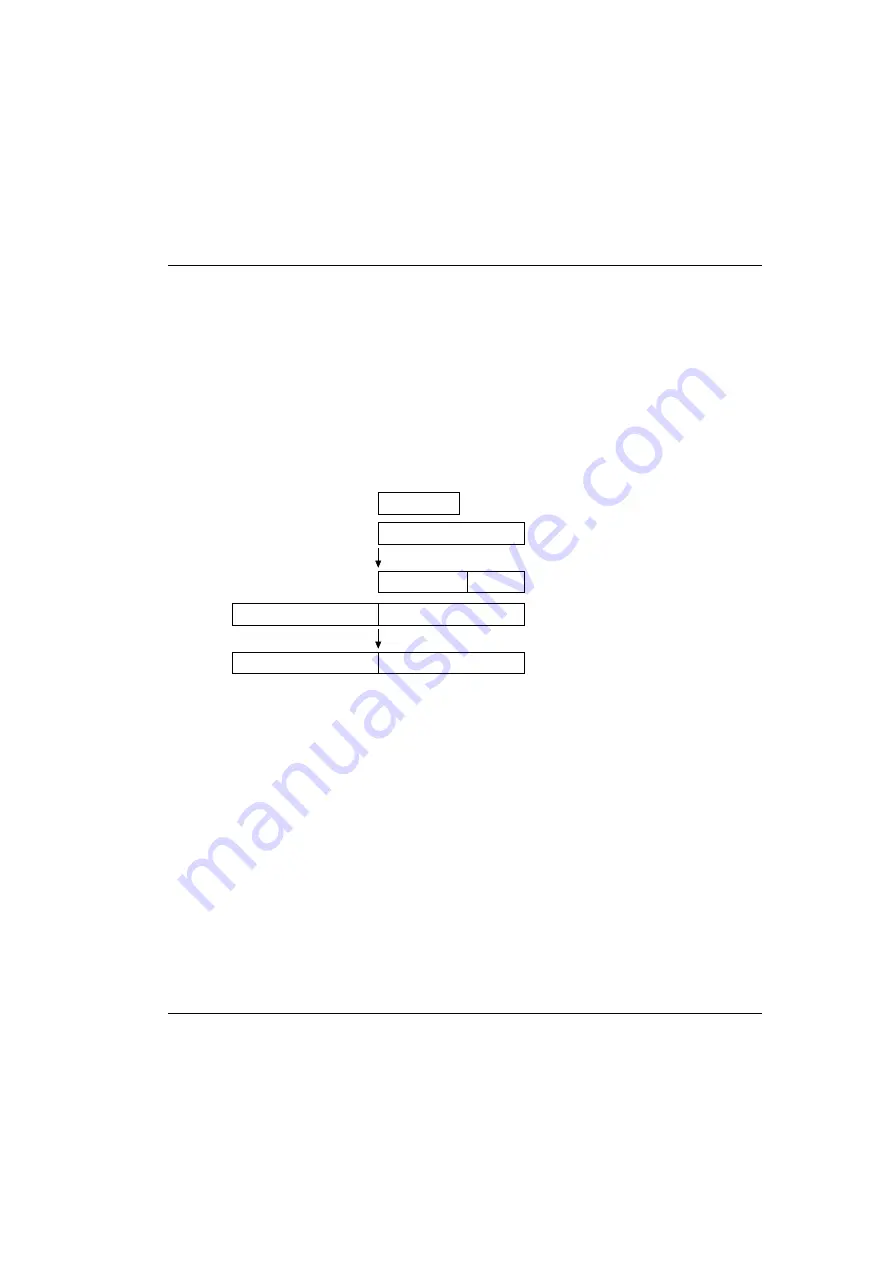

Example 2: Zero-extend divisor from 8 to 16 bits and dividend from 16 to 32 bits before dividing

EXTU.W

R0

; Zero-extend 8-bit divisor to 16 bits

BEQ

ZERODIV

; Branch to ZERODIV if R0 = 0

EXTU.L

ER1

; Zero-extend 16-bit dividend to 32 bits

EXTU.W

R0, ER1

; Divide using DIVXU.W

RTS

ZERODIV:

; Zero-divide handling routine

Instead of 16 bits ÷ 8 bits, the operation performed is 32 bits ÷ 16 bits

→

quotient (16 bits) and

remainder (16 bits), and no overflow occurs. The 16-bit quotient is stored in R1 and the 8-bit

remainder in the lower 8 bits of E1. The upper 8 bits of E1 are all 0.

ER1

R0L

R1

ER1

Divisor

Dividend

Sign extension

Sign extension

Dividend

Remainder

Quotient

Divisor

R0L

93