2.2.30 (1) EXTU (W)

EXTU (EXTend as Unsigned)

Zero Extension

Operation

0

→

(<bits 15 to 8> of Rd>)

Zero extend

Assembly-Language Format

EXTU.W

Rd

Operand Size

Word

Condition Code

H: Previous value remains unchanged.

N: Always cleared to 0.

Z: Set to 1 if the result is zero; otherwise

cleared to 0.

V: Always cleared to 0.

C: Previous value remains unchanged.

I

UI

H

U

N

Z

V

C

—

—

—

—

0

↕

0

—

Description

This instruction extends the lower 8 bits in a 16-bit register Rd to word data by padding with

zeros. That is, it clears the upper 8 bits of Rd (bits 15 to 8) to 0.

Available Registers

Rd: R0 to R7, E0 to E7

Operand Format and Number of States Required for Execution

Notes

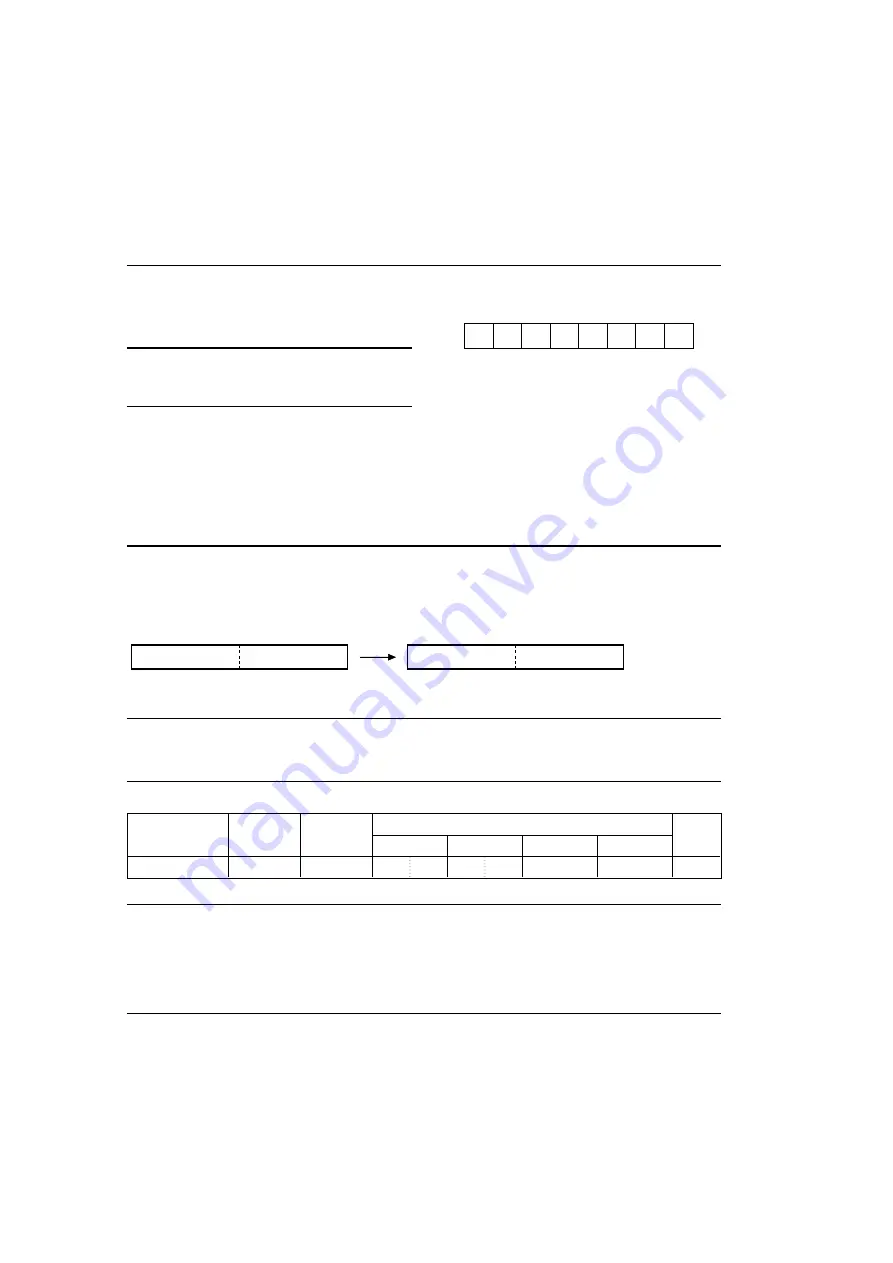

Don’t care

Rd

8 bits

8 bits

Zero extension

Rd

8 bits

8 bits

Instruction Format

1st byte

2nd byte

3rd byte

4th byte

Register direct

EXTU.W

Rd

1

7

5

rd

2

No. of

States

Addressing

Mode

Mnemonic

Operands

100