2.2.24 DAS

DAS (Decimal Adjust Subtract)

Decimal Adjust

Description

Given that the result of a subtraction operation performed by a SUB.B, SUBX.B, or NEG.B

instruction on 4-bit BCD data is contained in an 8-bit register Rd (destination register) and the

carry and half-carry flags, the DAS instruction adjusts the general register contents by adding

H'00, H'FA, H'A0, or H'9A according to the table below.

Available Registers

Rd: R0L to R7L, R0H to R7H

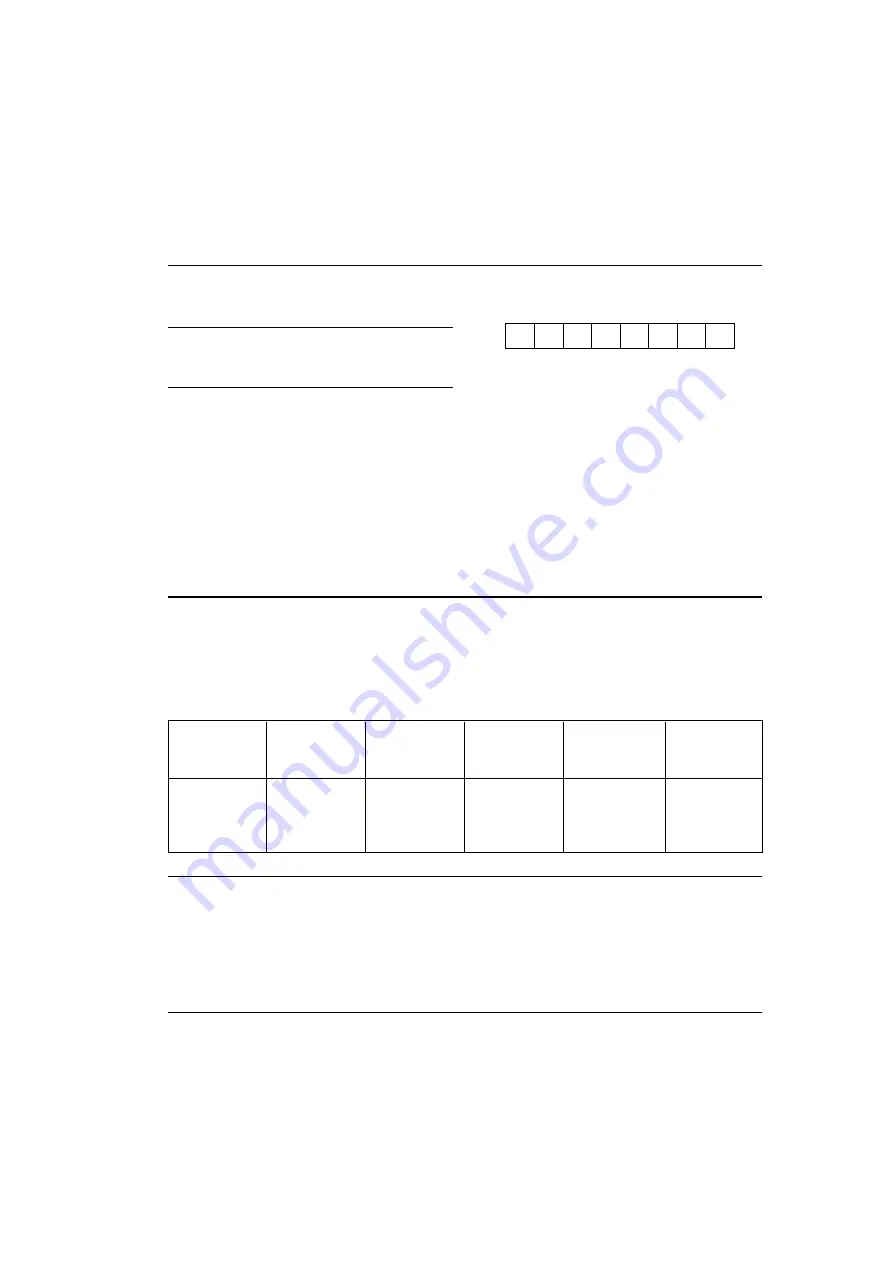

C Flag

Upper 4 Bits

H Flag

Lower 4 Bits

C Flag

before

before

before

before

after

Adjustment

Adjustment

Adjustment

Adjustment

Adjustment

0

0 to 9

0

0 to 9

00

0

0

0 to 8

1

6 to F

FA

0

1

7 to F

0

0 to 9

A0

1

1

6 to F

1

6 to F

9A

1

Value Added

(hexadecimal)

Operation

Rd (decimal adjust)

→

Rd

Assembly-Language Format

DAS

Rd

Operand Size

Byte

Condition Code

H: Undetermined (no guaranteed value).

N: Set to 1 if the adjusted result is negative;

otherwise cleared to 0.

Z: Set to 1 if the adjusted result is zero;

otherwise cleared to 0.

V: Undetermined (no guaranteed value).

C: Previous value remains unchanged.

I

UI

H

U

N

Z

V

C

—

—

*

—

↕

↕

*

—

77