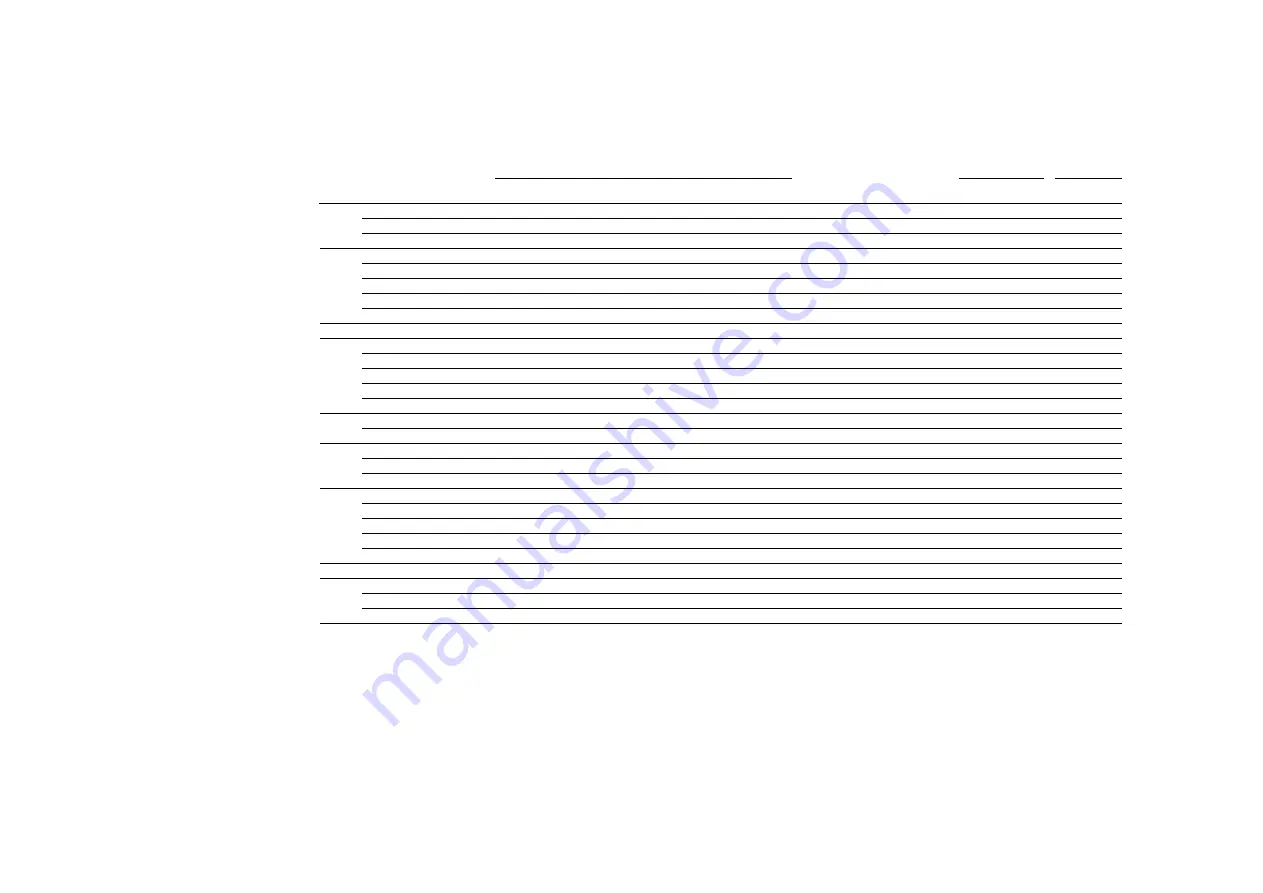

Table 2-2 Instruction Set (cont)

(2) Arithmetic Operation Instructions

Addressing Mode and Instruction Length (bytes)

Condition Code

No. of States

Ad-

Mnemonic

Size #xx Rn @ERn @(d,ERn) @ERn+/@–ERn @aa @(d,PC) @@aa —

Operation

I

H

N

Z V

C

Normal vanced

ADDS

ADDS.L #1,ERd

L

2

ERd32+1

→

ERd32

— — — — — —

2

2

ADDS.L #2,ERd

L

2

ERd32+2

→

ERd32

— — — — — —

2

2

ADDS.L #4,ERd

L

2

ERd32+4

→

ERd32

— — — — — —

2

2

INC

INC.B Rd

B

2

Rd8+1

→

Rd8

— —

↕

↕

↕

—

2

2

INC.W #1,Rd

W

2

Rd16+1

→

Rd16

— —

↕

↕

↕

—

2

2

INC.W #2,Rd

W

2

Rd16+2

→

Rd16

— —

↕

↕

↕

—

2

2

INC.L #1,ERd

L

2

ERd32+1

→

ERd32

— —

↕

↕

↕

—

2

2

INC.L #2,ERd

L

2

ERd32+2

→

ERd32

— —

↕

↕

↕

—

2

2

DAA

DAA Rd

B

2

Rd8 decimal adjust

→

Rd8

—

*

↕

↕

*

↕

2

2

SUB

SUB.B Rs,Rd

B

2

Rd8–Rs8

→

Rd8

—

↕

↕

↕

↕

↕

2

2

SUB.W #xx:16,Rd

W

4

Rd16–#xx:16

→

Rd16

—

1

↕

↕

↕

↕

4

4

SUB.W Rs,Rd

W

2

Rd16–Rs16

→

Rd16

—

1

↕

↕

↕

↕

2

2

SUB.L #xx:32,ERd

L

6

ERd32–#xx:32

→

ERd32

—

2

↕

↕

↕

↕

6

6

SUB.L ERs,ERd

L

2

ERd32–ERs32

→

ERd32

—

2

↕

↕

↕

↕

2

2

SUBX

SUBX.B #xx:8,Rd

B

2

Rd8–#xx:8–C

→

Rd8

—

↕

↕

3

↕

↕

2

2

SUBX.B Rs,Rd

B

2

Rd8–Rs8–C

→

Rd8

—

↕

↕

3

↕

↕

2

2

SUBS

SUBS.L #1,ERd

L

2

Erd32–1

→

ERd32

— — — — — —

2

2

SUBS.L #2,ERd

L

2

ERd32–2

→

ERd32

— — — — — —

2

2

SUBS.L #4,ERd

L

2

ERd32–4

→

ERd32

— — — — — —

2

2

DEC

DEC.B Rd

B

2

Rd8–1

→

Rd8

— —

↕

↕

↕

—

2

2

DEC.W #1,Rd

W

2

Rd16–1

→

Rd16

— —

↕

↕

↕

—

2

2

DEC.W #2,Rd

W

2

Rd16–2

→

Rd16

— —

↕

↕

↕

—

2

2

DEC.L #1,ERd

L

2

ERd32–1

→

ERd32

— —

↕

↕

↕

—

2

2

DEC.L #2,ERd

L

2

ERd32–2

→

ERd32

— —

↕

↕

↕

—

2

2

DAS

DAS Rd

B

2

Rd8 decimal adjust

→

Rd8

—

*

↕

↕

*

—

2

2

NEG

NEG.B Rd

B

2

0–Rd8

→

Rd8

—

↕

↕

↕

↕

↕

2

2

NEG.W Rd

W

2

0–Rd16

→

Rd16

—

↕

↕

↕

↕

↕

2

2

NEG.L ERd

L

2

0–ERd32-ERd32

—

↕

↕

↕

↕

↕

2

2

191