62

62

62

62

S I M U L A T E D C P U P O R T S ( P 0 , P 1 , P 2 , P 3 O F

F U J I T S U F L A S H C P U )

Registers

Base Address: 000000

H

for CPU native ports, 0000D8

H

for simulated CPU

ports

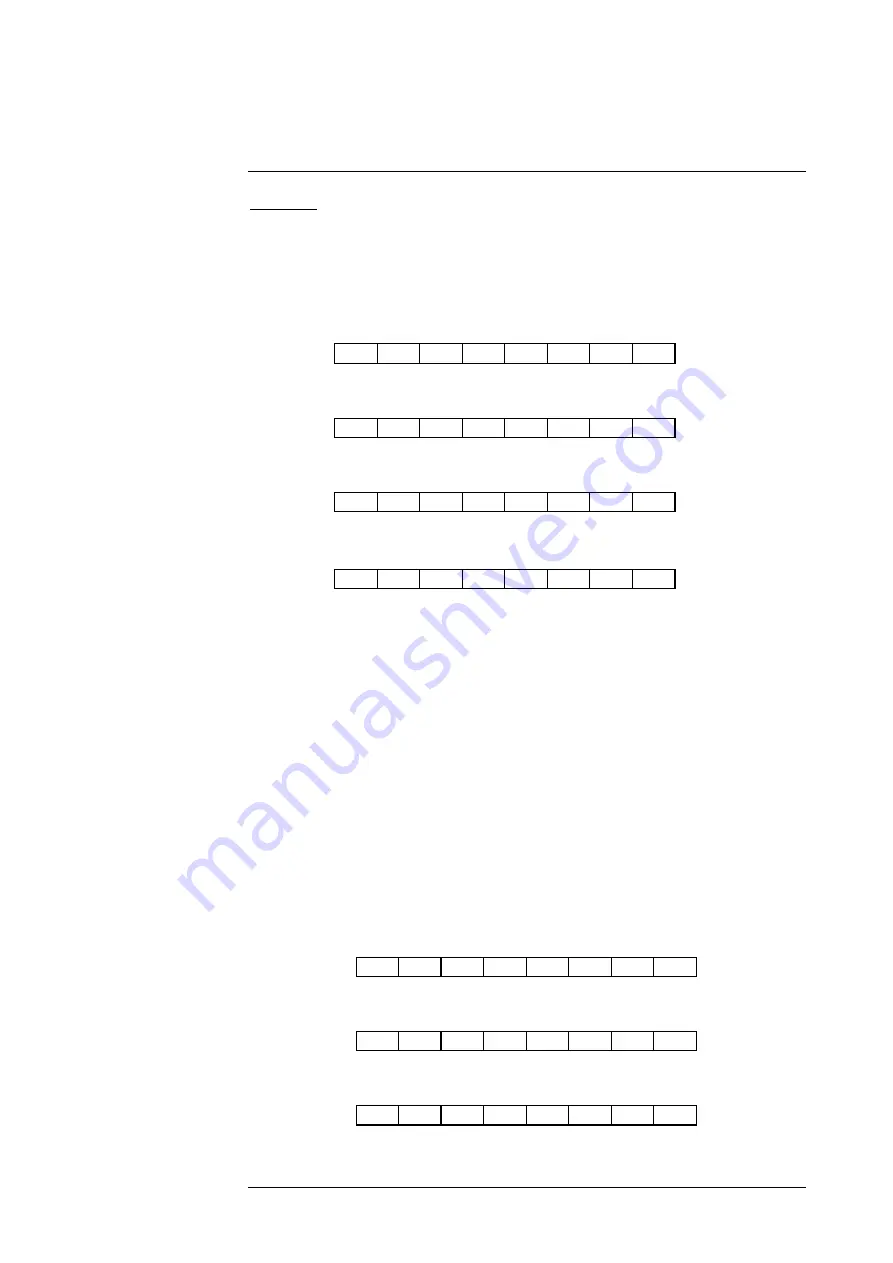

(1) Port data registers

PDR0

7

6

5

4

3

2

1

0

Initial

value

Acces

s

Addr.: D8

H

P07

P06

P05

P04

P03

P02

P01

P00

00

H

R/W

PDR1

15

14

13

12

11

10

9

8

Initial

value

Acces

s

Addr.: D9

H

P17

P16

P15

P14

P13

P12

P11

P10

00

H

R/W

PDR2

7

6

5

4

3

2

1

0

Initial

value

Acces

s

Addr: DA

H

P27

P26

P25

P24

P23

P22

P21

P20

00

H

R/W

PDR3

15

14

13

12

11

10

9

8

Initial

value

Acces

s

Addr:DB

H

P37

P36

P35

P34

P33

P32

P31

P30

00

H

R/W

Note: R/W for I/O ports means the following:

Input mode

Read: The level at the corresponding pin is read.

Write: Data is written to an output latch, but not to the pin.

Output mode

Read: The level at the corresponding pin is read. In most cases it will be the

value written to the pin as last, the only exception can happen when the

pin is erroneously pulled hard to VCC or GND.

Write: Data is written to an output latch and output to the corresponding pin.

(2) Port direction registers

DDR0

7

6

5

4

3

2

1

0

Initial

value

Acces

s

Addr.: DC

H

D07

D06

D05

D04

D03

D02

D01

D00

00

H

R/W

DDR1

15

14

13

12

11

10

9

8

Initial

value

Acces

s

Addr.: DD

H

D17

D16

D15

D14

D13

D12

D11

D10

00

H

R/W

DDR2

7

6

5

4

3

2

1

0

Initial

value

Acces

s

Addr.: DE

H

D27

D26

D25

D24

D23

D22

D21

D20

00

H

R/W