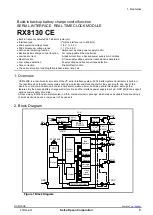

10. Interface timing when power is turned ON / OFF

RX8130CE

Jump to

ETM50E-07

Seiko Epson Corporation

16

10.3 V

DD

ON / OFF when using power switching (INIEN = 1)

See

4.1. Examples of power supply connection

Circuit EX1, 2, 3.

GND

t

R1

t

F

t

R2

+V

DET

11

t

CL

t

CU

+V

DET

11 or

+V

DET

12

Enabled

有効

-V

DET

11 or -

V

DET

12

Disabled

t

CD

POWER-ON-RESET

V

BAT

I

2

C Interface

V

CLK

Min.

V

DD

V

DET

2

Backup Mode

GND

(INIEN: 0 to 1)

I

2

C Access

Enabled

Initial power-On

Figure 13

Power-On sequence1

10.4 V

DD

ON / OFF when power switching is not used (INIEN = 0)

See

"4.1. Examples of power supply connection"

Circuit EX4.

t

R1

tF

t

CL

V

IO

Min. 1.6V

Enabled

t

CD

POWER-ON-RESET

I

2

C Interface

Disabled

Disabled

tR2

V

DD

V

IO

V

BAT

V

CLK

Min. 1.1V

Initial power-On

GND

Enabled

I

2

C Access

(INIEN: 1 to 0)

Figure 14

Power-On sequence2

Table 11 Power supply characteristics

Item

Symbol

Condition

Min.

Typ.

Max.

Unit

Power supply rise time

t

R1

From GND to V

DD

= +V

DET11

0.1

-

10

ms / V

Access wait time

t

CL

V

DD

= +V

DET11

to Access start

-

-30

ms

Access suspended time

t

CD

The time from the end of I

2

C access to the

disable of I

2

C

0

-

-

ms

Power supply fall time

t

F

From V

DD

to V

DD

= V

CLK

1

-

-

ms / V

Power supply rise time

t

R2

Time to restore V

DD

to operating voltage

1

-

-

ms / V

Access wait time

t

CU

V

DD

=+V

DET1x

to Access start

-

35

ms

tR1, tR2, and tF specify that there is no voltage fluctuation faster / slower than the Min / Max specifications within the specified section.

The risk when specifications were not satisfied, refer to the following.

Item

Risk of fast fluctuations

Risk of slow fluctuations

tR1

Power-On-Reset doesn't occur.

tR2

The FOUT waveform disappears momentarily,

and clock time is momentarily delayed.

A data of RTC loss. A set of VLF.

None

tF

V

DD

and V

BAT

in Figures 13 and 14 are the voltages of V

DD

and V

BAT

pins of RX8130CE.

Regarding access to the clock register after the initial power-on,

, See

"10.1 restrictions of I2C interface in the initial power on"

The clock from FOUT is outputted after tCU.

When status of V

DD

= V

BAT

= GND doesn't keep more than 10seconds before initial power-on, the Power-On-Reset may not work even if

the tR / tF specifications are satisfied.