SARA-G450 - System integration manual

UBX-18046432 - R08

System description

Page 40 of 143

C1-Public

1.9.2

Secondary auxiliary serial interface (AUX UART)

☞

Secondary auxiliary UART interface is not supported by the “00” product version. This interface

should be left unconnected and should not be driven by external devices.

The secondary auxiliary UART interface (AUX UART) is a 3-wire unbalanced asynchronous serial

interface available over RXD_AUX (data output pin) and TXD_AUX (data input pin), supporting:

AT command mode

11

Data mode and online command mode

GNSS tunneling

SARA-G450 modules’ auxiliary UART interface is configured by default for AT commands.

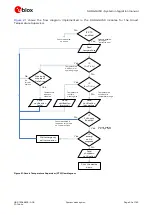

The serial interface configuration can be changed by means of the +USIO AT command to select

different alternative serial interface configuration variants, summarized in

, available in a

mutually exclusive way (for more details, see the u-blox AT commands manual

, +USIO AT

command).

AT+USIO UART

AUX UART

FT UART

Remarks

0

AT, data and MUX

AT, data

Diagnostic

1

AT, data and MUX

AT, data

Diagnostic

Default configuration

2

AT, data and MUX

AT, data

Diagnostic

3

AT, data and MUX

GNSS tunneling

Diagnostic

4

AT, data and MUX

GNSS tunneling

Diagnostic

Table 10: Alternative serial interface configuration variants supported by SARA-G4 modules product versions “01” onwards

☞

The serial interface configuration cannot be changed on the “00” product version of the

SARA-G450 modules: the +USIO AT command is not supported.

SARA-G450 modules’ auxiliary UART interface can be configured in AT command mode by means of

the AT+USIO command (for more details, see

) so that:

the cellular module waits for AT command instructions and interprets all the characters received

over the auxiliary UART interface as commands to be executed

the auxiliary UART interface provides RS-232 functionality conforming to ITU-T V.24

recommendation

with CMOS compatible signal levels: 0 V for low data bit or ON state and

1.8 V / 3 V for high data bit or OFF state (for detailed electrical characteristics, see the SARA-G450

data sheet

the cellular module is designed to operate as a modem, which represents the Data

Circuit-terminating Equipment (DCE) according to ITU-T V.24 recommendation

: the

application processor connected to the module through the auxiliary UART interface represents

the Data Terminal Equipment (DTE)

Flow control is not supported

2400, 4800, 9600, 19200, 38400, 57600 and 115200 bit/s baud rates can be set (see the u-blox AT

commands manual

, +IPR)

8N1, 8E1, 8O1 or 8N2 frame format can be set (see the u-blox AT commands manual

, +ICF)

11

See the u-blox AT commands manual

for the definition of the command mode, data mode, and online command mode.