SARA-G450 - System integration manual

UBX-18046432 - R08

Appendix

Page 127 of 143

C1-Public

Appendix

A

Migration between SARA modules

A.1

Overview

The u-blox SARA form factor (26.0 x 16.0 mm, 96-pin LGA) includes the following series of modules,

with compatible pin assignments as described in

, so that the modules can be alternatively

mounted on a single application PCB using exactly the same copper, solder resist and paste mask:

SARA-R41x modules supporting LTE Cat M1, LTE Cat NB1 and 2G radio access technologies

SARA-R42x modules supporting LTE Cat M1, LTE Cat NB2 and 2G radio access technologies

SARA-R5xx modules supporting LTE Cat M1 and LTE Cat NB2 radio access technologies

SARA-N2xx modules supporting LTE Cat NB1 radio access technology

SARA-N3xx modules supporting LTE Cat NB2 radio access technology

SARA-G3xx modules supporting 2G radio access technology

SARA-G4xx modules supporting 2G radio access technology

SARA-U2xx modules supporting 3G and 2G radio access technologies

64 63

61 60

58 57

55 54

22 23

25 26

28 29

31 32

11

10

8

7

5

4

2

1

21

19

18

16

15

13

12

43

44

46

47

49

50

52

53

33

35

36

38

39

41

42

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

CTS

RTS

DCD

RI

V_INT

V_BCKP

GND

RSVD

RESET_N

GPIO1

PWR_ON

RXD

TXD

3

20

17

14

9

6

24

27

30

51

48

45

40

37

34

59

62

56

GND

GND

DSR

DTR

GND

RSVD

GND

GND

RX

D

_A

UX

T

XD

_A

UX

RS

V

D

G

N

D

G

PIO2

G

PIO3

S

D

A

S

CL

G

PIO4

G

N

D

G

N

D

GND

SPK_P

MIC_BIAS

MIC_GND

MIC_P

GND

VCC

VCC

RSVD

I2S_TXD

I2S_CLK

SIM_CLK

SIM_IO

VSIM

SIM_DET

VCC

MIC_N

SPK_N

SIM_RST

I2S_RXD

I2S_WA

G

N

D

G

N

D

G

N

D

G

N

D

G

N

D

G

N

D

G

N

D

G

N

D

G

N

D

A

N

T

_D

E

T

A

N

T

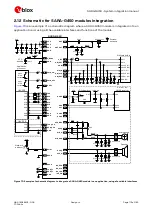

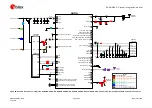

SARA-G3xx

Top view

Pin 65-96: GND

64 63

61 60

58 57

55 54

22 23

25 26

28 29

31 32

11

10

8

7

5

4

2

1

21

19

18

16

15

13

12

43

44

46

47

49

50

52

53

33

35

36

38

39

41

42

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

CTS

RTS

DCD

RI

V_INT

V_BCKP

GND

CODEC_CLK

RESET_N

GPIO1

PWR_ON

RXD

TXD

3

20

17

14

9

6

24

27

30

51

48

45

40

37

34

59

62

56

GND

GND

DSR

DTR

GND

VUSB_DET

GND

GND

US

B

_D

-

US

B

_D

+

RS

V

D

G

N

D

G

PIO2

G

PIO3

S

D

A

S

CL

G

PIO4

G

N

D

G

N

D

GND

RSVD

RSVD

RSVD

RSVD

GND

VCC

VCC

RSVD

I2S_TXD

I2S_CLK

SIM_CLK

SIM_IO

VSIM

SIM_DET

VCC

RSVD

RSVD

SIM_RST

I2S_RXD

I2S_WA

G

N

D

G

N

D

G

N

D

G

N

D

G

N

D

G

N

D

G

N

D

G

N

D

G

N

D

A

N

T

_D

E

T

A

N

T

SARA-U2xx

Top view

Pin 65-96: GND

64 63

61 60

58 57

55 54

22 23

25 26

28 29

31 32

11

10

8

7

5

4

2

1

21

19

18

16

15

13

12

43

44

46

47

49

50

52

53

33

35

36

38

39

41

42

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

CTS

RTS

DCD

RI

V_INT

V_BCKP

GND

RXD_AUX

PWR_OFF

GPIO1

PWR_ON

RXD

TXD

3

20

17

14

9

6

24

27

30

51

48

45

40

37

34

59

62

56

GND

GND

DSR

DTR

GND

TXD_AUX

GND

VSEL

RX

D

_F

T

T

XD

_F

T

RS

V

D

G

N

D

G

PIO2

G

PIO3

S

D

A

S

CL

G

PIO4

G

N

D

G

N

D

GND

SPK_P

MIC_BIAS

MIC_GND

MIC_P

GND

VCC

VCC

RSVD

I2S_TXD

I2S_CLK

SIM_CLK

SIM_IO

VSIM

SIM_DET

VCC

MIC_N

SPK_N

SIM_RST

I2S_RXD

I2S_WA

G

N

D

G

N

D

G

N

D

G

N

D

G

N

D

G

N

D

G

N

D

G

N

D

G

N

D

A

N

T

_D

E

T

A

N

T

SARA-G4xx

Top view

Pin 65-96: GND

64 63

61 60

58 57

55 54

22 23

25 26

28 29

31 32

11

10

8

7

5

4

2

1

21

19

18

16

15

13

12

43

44

46

47

49

50

52

53

33

35

36

38

39

41

42

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

CTS

RTS

RSVD

RSVD

V_INT

RSVD

GND

RSVD

RESET_N

GPIO1

RSVD

RXD

TXD

3

20

17

14

9

6

24

27

30

51

48

45

40

37

34

59

62

56

GND

GND

RSVD

RSVD

GND

RSVD

GND

GND

RS

V

D

RS

V

D

RS

V

D

G

N

D

RS

V

D

G

PIO2

S

D

A

S

CL

RS

V

D

G

N

D

G

N

D

GND

RSVD

RSVD

RSVD

RSVD

GND

VCC

VCC

RSVD

RSVD

RSVD

SIM_CLK

SIM_IO

VSIM

RSVD

VCC

RSVD

RSVD

SIM_RST

RSVD

RSVD

G

N

D

G

N

D

G

N

D

G

N

D

G

N

D

G

N

D

G

N

D

G

N

D

G

N

D

A

N

T

_D

E

T

A

N

T

SARA-N2xx

Top view

Pin 65-96: GND

64 63

61 60

58 57

55 54

22 23

25 26

28 29

31 32

11

10

8

7

5

4

2

1

21

19

18

16

15

13

12

43

44

46

47

49

50

52

53

33

35

36

38

39

41

42

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

CTS

RTS

DCD

RI

V_INT

V_BCKP

GND

RXD_AUX

RESET_N

GPIO1

PWR_ON

RXD

TXD

3

20

17

14

9

6

24

27

30

51

48

45

40

37

34

59

62

56

GND

GND

DSR

DTR

GND

TXD_AUX

GND

VSEL

RX

D

_F

T

T

XD

_F

T

RS

V

D

G

N

D

G

PIO2

G

PIO3

S

D

A

S

CL

G

PIO4

G

N

D

G

N

D

GND

RSVD

RSVD

RSVD

RSVD

GND

VCC

VCC

ADC1

RSVD

RSVD

SIM_CLK

SIM_IO

VSIM

GPIO5

VCC

RSVD

RSVD

SIM_RST

RSVD

RSVD

G

N

D

G

N

D

G

N

D

G

N

D

G

N

D

G

N

D

G

N

D

G

N

D

A

N

T

_B

T

A

N

T

_D

E

T

A

N

T

SARA-N3xx

Top view

Pin 65-96: GND

64 63

61 60

58 57

55 54

22 23

25 26

28 29

31 32

11

10

8

7

5

4

2

1

21

19

18

16

15

13

12

43

44

46

47

49

50

52

53

33

35

36

38

39

41

42

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

CTS

RTS

DCD

RI

V_INT

RSVD

GND

GPIO6

RESET_N

GPIO1

PWR_ON

RXD

TXD

3

20

17

14

9

6

24

27

30

51

48

45

40

37

34

59

62

56

GND

GND

DSR

DTR

GND

VUSB_DET

GND

GND

US

B

_D

-

US

B

_D

+

RS

V

D

G

N

D

G

PIO2

G

PIO3

S

D

A

S

CL

G

PIO4

G

N

D

G

N

D

GND

SDIO_D2

SDIO_CMD

SDIO_D0

SDIO_D1

GND

VCC

VCC

RSVD

I2S_TXD/SPI_CS

I2S_CLK/SPI_CLK

SIM_CLK

SIM_IO

VSIM

GPIO5

VCC

SDIO_D3

SDIO_CLK

SIM_RST

I2S_RXD/SPI_MISO

I2S_WA/SPI_MOSI

G

N

D

G

N

D

G

N

D

G

N

D

G

N

D

G

N

D

G

N

D

G

N

D

G

N

D

A

N

T

_D

E

T

A

N

T

SARA-R41x

Top view

Pin 65-96: GND

64 63

61 60

58 57

55 54

22 23

25 26

28 29

31 32

11

10

8

7

5

4

2

1

21

19

18

16

15

13

12

43

44

46

47

49

50

52

53

33

35

36

38

39

41

42

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

CTS

RTS

DCD

RI

V_INT

RSVD

GND

GPIO6

RESET_N

GPIO1

PWR_ON

RXD

TXD

3

20

17

14

9

6

24

27

30

51

48

45

40

37

34

59

62

56

GND

GND

DSR

DTR

GND

VUSB_DET

GND

GND

US

B

_D

-

US

B

_D

+

A

N

T

_G

N

S

S

G

N

D

G

PIO2

G

PIO3

S

D

A

S

CL

G

PIO4

G

N

D

G

N

D

GND

SDIO_D2

SDIO_CMD

SDIO_D0

SDIO_D1

GND

VCC

VCC

EXT_INT

I2S_TXD

I2S_CLK

SIM_CLK

SIM_IO

VSIM

GPIO5

VCC

SDIO_D3

SDIO_CLK

SIM_RST

I2S_RXD

I2S_WA

G

N

D

G

N

D

G

N

D

G

N

D

G

N

D

G

N

D

G

N

D

G

N

D

G

N

D

A

N

T

_D

E

T

A

N

T

SARA-R5xx

Top view

Pin 65-96: GND

64 63

61 60

58 57

55 54

22 23

25 26

28 29

31 32

11

10

8

7

5

4

2

1

21

19

18

16

15

13

12

43

44

46

47

49

50

52

53

33

35

36

38

39

41

42

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

CTS

RTS

DCD

RI

V_INT

USB_3V3

GND

GPIO6

RSVD

GPIO1

PWR_CTRL

RXD

TXD

3

20

17

14

9

6

24

27

30

51

48

45

40

37

34

59

62

56

GND

GND

DSR

DTR

GND

USB_5V0

GND

GND

US

B

_D

-

US

B

_D

+

A

N

T

_G

N

S

S

G

N

D

G

PIO2

G

PIO3

S

D

A

S

CL

G

PIO4

G

N

D

G

N

D

GND

ANT_ON

EXTINT

RSVD

RSVD

GND

VCC

VCC

RSVD

I2S_TXD

I2S_CLK

SIM_CLK

SIM_IO

VSIM

GPIO5

VCC

RSVD

TIMEPULSE

SIM_RST

I2S_RXD

I2S_WA

G

N

D

G

N

D

G

N

D

G

N

D

G

N

D

G

N

D

G

N

D

G

N

D

G

N

D

A

N

T

_D

E

T

A

N

T

SARA-R42x

Top view

Pin 65-96: GND

Figure 75: SARA-R4, SARA-R5, SARA-N2, SARA-N3, SARA-G3, SARA-G4, and SARA-U2 modules’ layout and pin assignment