SARA-G3 series - System Integration Manual

UBX-13000995 - R06

Objective Specification

Design-in

Page 127 of 218

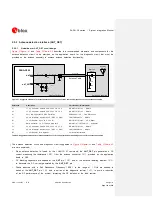

Connect the other pin of the mechanical switch integrated in the two SIM connectors (e.g. the SW1

pins as described in

) to the

V_INT

1.8 V supply output of the module by means

of a strong (e.g. 1 k

) pull-up resistor, as the R1 and R3 resistors in

Provide a weak (e.g. 470 k

) pull-down resistor at the SIM detection line, between the double-

throw digital switch and the related SIM connector as the R2 and R4 resistors in

Provide a 100 nF bypass capacitor (e.g. Murata GRM155R71C104K) at the SIM supply line

(

VSIM

), close to the relevant pad of the two SIM connectors, to prevent digital noise

Provide a bypass capacitor of about 22 pF to 47 pF (e.g. Murata GRM1555C1H470J) on each SIM

line (

VSIM

,

SIM_CLK

,

SIM_IO

,

SIM_RST

), very close to each relevant pad of the two SIM

connectors, to prevent RF coupling especially in case the RF antenna is placed closer than 10 - 30

cm from the SIM card holders

Provide a very low capacitance (i.e. less than 10 pF) ESD protection (e.g. Tyco Electronics

PESD0402-140) on each externally accessible SIM line, close to each relevant pad of the two SIM

connectors, according to the EMC/ESD requirements of the custom application

Limit capacitance and series resistance on each SIM signal (

SIM_CLK

,

SIM_IO

,

SIM_RST

) to match

the requirements for the SIM interface (27.7 ns is the maximum allowed rise time on the

SIM_CLK

line, 1.0 µs is the maximum allowed rise time on the

SIM_IO

and

SIM_RST

lines)

SARA-G3 series

C1

FIRST

SIM CARD

HOLDER

VPP (C6)

VCC (C1)

IO (C7)

CLK (C3)

RST (C2)

GND (C5)

C2

C3

C5

J1

C4

SW1

SW2

D1 D2 D3 D4 D5 D6

GND

U1

41

VSIM

VSIM

1VSIM

2VSIM

VCC

C11

4PDT

Analog

Switch

3V8

39

SIM _IO

DAT

1DAT

2DAT

38

SIM _CLK

CLK

1CLK

2CLK

40

SIM _RST

RST

1RST

2RST

SEL

Y

GND

U2

I0

I1

VCC

SPDT

Digital

Switch

S

42

SIM _DET

4

V_INT

C12

R4

R3

SECOND

SIM CARD

HOLDER

VPP (C6)

VCC (C1)

IO (C7)

CLK (C3)

RST (C2)

GND (C5)

J2

SW1

SW2

C6

C7

C8

C10

C9

D7 D8 D9 D10 D11 D12

R2

R1

Application

Processor

GPIO

R5

TP

Figure 46: Application circuit for the connection to two removable SIM cards, with SIM detection implemented