1

2

14

15

16

17

25

26

27

28

29

30

31

32

SCLK

CS

D9

D8

D7

D6

D5

D4

SDO

Sample

N

Sample

N + 1

Data from sample N

33

34

D17

D16

18

D3

D2

D1

D0

B15

B14

B2

B1

B0

X X X X X X X X X

SDI

7

8

9

B9

B8

B7

B10

B3

1

2

3

4

SBAS686 – JULY 2015

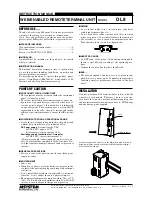

8.4.1.2 Data Acquisition Example

This section provides an example of how a host processor can use the device interface to configure the device

internal registers as well as convert and acquire data for sampling a particular input channel. The timing diagram

shown in

provides further details.

Figure 75. Device Operation Using the Serial Interface Timing Diagram

There are four events shown in

. These events are described below:

•

Event 1:

The host initiates a data conversion frame through a falling edge of the CS signal. The analog input

signal at the instant of the CS falling edge is sampled by the ADC and conversion is performed using an

internal oscillator clock. The analog input channel converted during this frame is selected in the previous data

frame. The internal register settings of the device for the next conversion can be input during this data frame

using the SDI and SCLK inputs. Initiate SCLK at this instant and latch data on the SDI line into the device on

every SCLK falling edge for the next 16 SCLK cycles. At this instant, SDO goes low because the device does

not output internal conversion data on the SDO line during the first 16 SCLK cycles.

•

Event 2:

During the first 16 SCLK cycles, the device completes the internal conversion process and data are

now ready within the converter. However, the device does not output data bits on SDO until the 16th falling

edge appears on the SCLK input. Because the ADC conversion time is fixed (the maximum value is given in

the

table), the 16th SCLK falling edge must appear after the internal conversion is

over, otherwise data output from the device is incorrect. Therefore, the SCLK frequency cannot exceed a

maximum value, as provided in the

Timing Requirements: Serial Interface

table.

•

Event 3:

At the 16th falling edge of the SCLK signal, the device reads the LSB of the input word on the SDI

line. The device does not read anything from the SDI line for the remaining data frame. On the same edge,

the MSB of the conversion data is output on the SDO line and can be read by the host processor on the

subsequent falling edge of the SCLK signal. For 18 bits of output data, the LSB can be read on the 34th

SCLK falling edge. The SDO outputs 0 on subsequent SCLK falling edges until the next conversion is

initiated.

•

Event 4:

When the internal data from the device is received, the host terminates the data frame by

deactivating the CS signal to high. The SDO output goes into a Hi-Z state until the next data frame is initiated,

as explained in Event 1.

8.4.1.3 Host-to-Device Connection Topologies

The digital interface of the ADS8694 and ADS8698 offers a lot of flexibility in the ways that a host controller can

exchange data or commands with the device. A typical connection between a host controller and a stand-alone

device is illustrated in

. However, there are applications that require multiple ADCs but the host

controller has limited interfacing capability. This section describes two connection topologies that can be used to

address the requirements of such applications.

36

Copyright © 2015, Texas Instruments Incorporated

Product Folder Links: